CPU 基本知識

CPU是計算機的大腦。

1、程序的運行過程,實際上是程序涉及到的、未涉及到的一大堆的指令的執(zhí)行過程。

當程序要執(zhí)行的部分被裝載到內(nèi)存后,CPU要從內(nèi)存中取出指令,然后指令解碼(以便知道類型和操作數(shù),簡單的理解為CPU要知道這是什么指令),然后執(zhí)行該指令。再然后取下一個指令、解碼、執(zhí)行,以此類推直到程序退出。

2、這個取指、解碼、執(zhí)行三個過程構(gòu)成一個CPU的基本周期。

3、每個CPU都有一套自己可以執(zhí)行的專門的指令集(注意,這部分指令是CPU提供的,CPU-Z軟件可查看)。

正是因為不同CPU架構(gòu)的指令集不同,使得x86處理器不能執(zhí)行ARM程序,ARM程序也不能執(zhí)行x86程序。(Intel和AMD都使用x86指令集,手機絕大多數(shù)使用ARM指令集)。

注:指令集的軟硬件層次之分:硬件指令集是硬件層次上由CPU自身提供的可執(zhí)行的指令集合。軟件指令集是指語言程序庫所提供的指令,只要安裝了該語言的程序庫,指令就可以執(zhí)行。

4、由于CPU訪問內(nèi)存以得到指令或數(shù)據(jù)的時間要比執(zhí)行指令花費的時間長很多,因此在CPU內(nèi)部提供了一些用來保存關(guān)鍵變量、臨時數(shù)據(jù)等信息的通用寄存器。

所以,CPU需要提供 一些特定的指令,使得可以從內(nèi)存中讀取數(shù)據(jù)存入寄存器以及可以將寄存器數(shù)據(jù)存入內(nèi)存。

此外還需要提供加法、減、not/and/or等基本運算指令,而乘除法運算都是推算出來的(支持的基本運算指令參見ALU Functions),所以乘除法的速度要慢的多。這也是算法里在考慮時間復雜度時常常忽略加減法次數(shù)帶來的影響,而考慮乘除法的次數(shù)的原因。

5、除了通用寄存器,還有一些特殊的寄存器。典型的如:

PC:program counter,表示程序計數(shù)器,它保存了將要取出的下一條指令的內(nèi)存地址,指令取出后,就會更新該寄存器指向下一條指令。 堆棧指針:指向內(nèi)存當前棧的頂端,包含了每個函數(shù)執(zhí)行過程的棧幀,該棧幀中保存了該函數(shù)相關(guān)的輸入?yún)?shù)、局部變量、以及一些沒有保存在寄存器中的臨時變量。 PSW:program status word,表示程序狀態(tài)字,這個寄存器內(nèi)保存了一些控制位,比如CPU的優(yōu)先級、CPU的工作模式(用戶態(tài)還是內(nèi)核態(tài)模式)等。

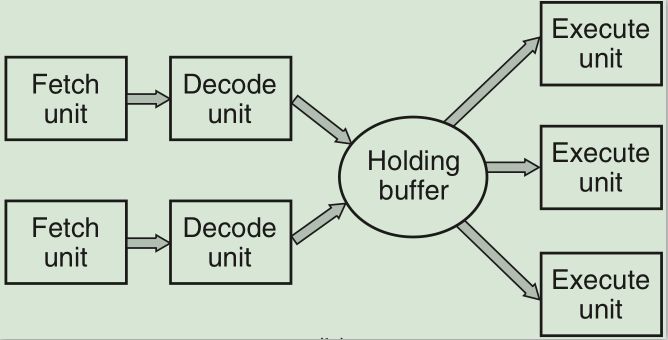

取指-->解碼-->執(zhí)行的路線,而是分別為這3個過程分別提供獨立的取值單元,解碼單元以及執(zhí)行單元。這樣就形成了流水線模式。例如,流水線的最后一個單元——執(zhí)行單元正在執(zhí)行第n條指令,而前一個單元可以對第n+1條指令進行解碼,再前一個單元即取指單元可以去讀取第n+2條指令。這是三階段的流水線,還可能會有更長的流水線模式。

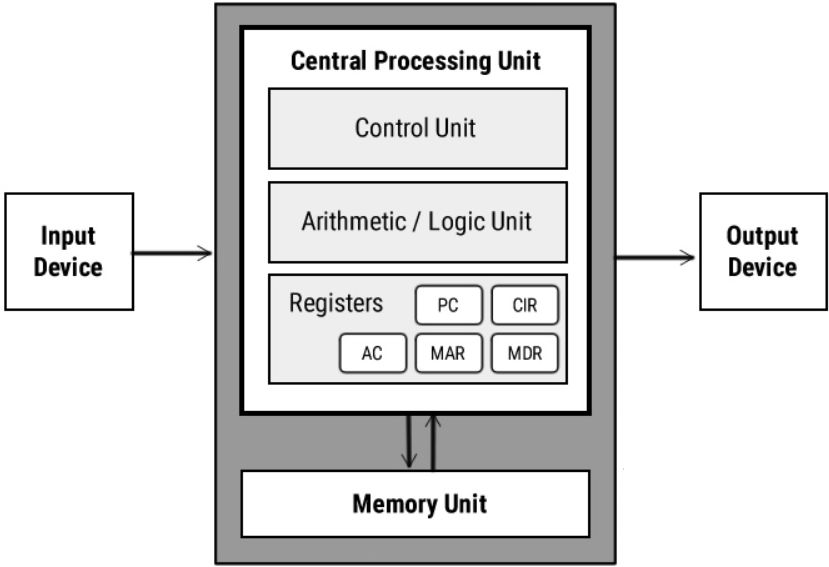

關(guān)于CPU的基本組成

c=a+b。MAR: memory address register,保存將要被訪問數(shù)據(jù)在內(nèi)存中哪個地址處,保存的是地址值 MDR: memory data register,保存從內(nèi)存讀取進來的數(shù)據(jù)或?qū)⒁獙懭雰?nèi)存的數(shù)據(jù),保存的是數(shù)據(jù)值 AC: Accumulator,保存算術(shù)運算和邏輯運算的中間結(jié)果,保存的是數(shù)據(jù)值 PC: Program Counter,保存下一個將要被執(zhí)行指令的地址,保存的是地址值 CIR: current instruction register,保存當前正在執(zhí)行的指令

控制器還包含了一些控制信號。

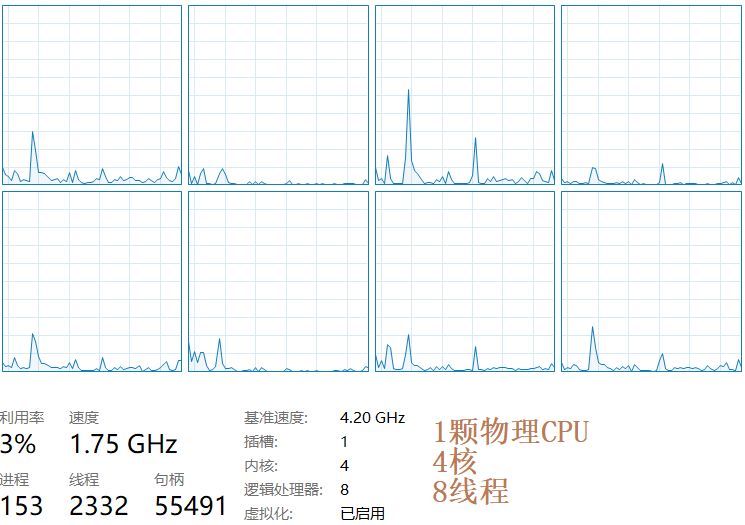

關(guān)于CPU的多核和多線程

這是欺騙操作系統(tǒng)的行為,在物理上仍然只有1核,只不過在超線程CPU的角度上看,它認為它的超線程會加速程序的運行。

例如,假設(shè)每核CPU都只有一個"發(fā)動機"資源,那么線程1這個虛擬CPU使用了這個"發(fā)動機"后,線程2就沒法使用,只能等待。

所以,超線程技術(shù)的主要目的是為了增加流水線(參見前文對流水線的解釋)上更多個獨立的指令,這樣線程1和線程2在流水線上就盡量不會爭搶該核CPU資源。所以,超線程技術(shù)利用了superscalar(超標量)架構(gòu)的優(yōu)點。

但是,線程1和線程2在很多方面上是可以并行執(zhí)行的。比如可以并行取指、并行解碼、并行執(zhí)行指令等。所以雖然單核在同一時間只能執(zhí)行一個進程,但線程1和線程2可以互相幫助,加速進程的執(zhí)行。

并且,如果線程1在某一時刻獲取了該核執(zhí)行進程的能力,假設(shè)此刻該進程發(fā)出了IO請求,于是線程1掌握的執(zhí)行進程的能力,就可以被線程2獲取,即切換到線程2。這是在執(zhí)行線程間的切換,是非常輕量級的。(WIKI: if resources for one process are not available, then another process can continue if its resources are available)

關(guān)于CPU上的高速緩存

32bit:32*32比特=128字節(jié) 64bit:64*64比特=512字節(jié)

- 推薦閱讀 -

《架構(gòu)師離職后,成為自由開發(fā)者的第 100 天》

往期推薦

下方二維碼關(guān)注我

互聯(lián)網(wǎng)草根,堅持分享技術(shù)、創(chuàng)業(yè)、產(chǎn)品等心得和總結(jié)~

點擊“閱讀原文”,領(lǐng)取 2020 年最新免費技術(shù)資料大全