總結(jié)了一份嵌入式硬件開發(fā)的具體流程

來源:網(wǎng)絡(luò)素材

整理:李肖遙

傳送門 : 總結(jié)了一份嵌入式產(chǎn)品研發(fā)的具體流程

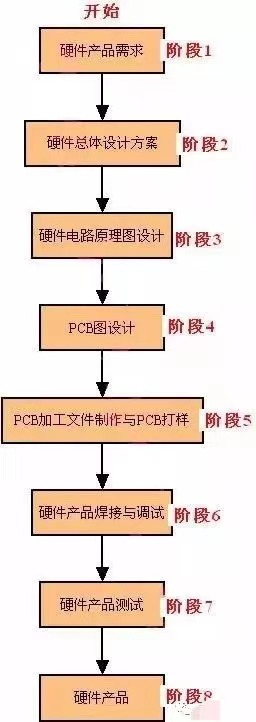

之前,我們?cè)敿?xì)講述了嵌入式產(chǎn)品的研發(fā)流程,那么在這一節(jié),我們具體以嵌入式產(chǎn)品的硬件部分為例,再次講解其開發(fā)過程,希望通過這一節(jié),大家能對(duì)嵌入式硬件開發(fā)流程有更深刻的認(rèn)識(shí),在以后的學(xué)習(xí)和工作中,更加規(guī)范化和標(biāo)準(zhǔn)化,提高開發(fā)技能。嵌入式硬件開發(fā)流程一般如下圖,分為8個(gè)階段:

嵌入式產(chǎn)品的硬件形態(tài)各異,CPU 從簡(jiǎn)單的4 位/8位單片機(jī)到32 位的ARM處理器,以及其他專用IC。另外,依據(jù)產(chǎn)品的不同需求,外圍電路也各不相同。每一次硬件開發(fā)過程,都需要依據(jù)實(shí)際的需求,考慮多方面的因素,選擇最合適的方案來。

硬件階段1:硬件產(chǎn)品需求

和普通的嵌入式產(chǎn)品需求一樣。階段1:產(chǎn)品需求。

硬件階段2:硬件總體設(shè)計(jì)方案

一個(gè)硬件開發(fā)項(xiàng)目,它的需求可能來自很多方面,比如市場(chǎng)產(chǎn)品的需要或性能提升的要求等,因此,作為一個(gè)硬件設(shè)計(jì)人員,我們需要主動(dòng)去了解各個(gè)方面的需求并分析,根據(jù)系統(tǒng)所要完成的功能,選擇最合適的硬件方案。

在這一階段,我們需要分析整個(gè)系統(tǒng)設(shè)計(jì)的可行性,包括方案中主要器件的可采購(gòu)性,產(chǎn)品開發(fā)投入,項(xiàng)目開發(fā)周期預(yù)計(jì),開發(fā)風(fēng)險(xiǎn)評(píng)估等,并針對(duì)開發(fā)過程中可能遇到的問題,提前選擇應(yīng)對(duì)方案,保證硬件的順利完成。

硬件階段3:硬件電路原理圖設(shè)計(jì)

在系統(tǒng)方案確定后,我們即可以開展相關(guān)的設(shè)計(jì)工作,原理設(shè)計(jì)主要包括系統(tǒng)總體設(shè)計(jì)和詳細(xì)設(shè)計(jì),最終產(chǎn)生詳細(xì)的設(shè)計(jì)文檔和硬件原理圖。

原理設(shè)計(jì)和PCB設(shè)計(jì)是設(shè)計(jì)人員最主要的兩個(gè)工作之一,在原理設(shè)計(jì)過程中,我們需要規(guī)劃硬件內(nèi)部資源,如系統(tǒng)存儲(chǔ)空間,以及各個(gè)外圍電路模塊的實(shí)現(xiàn)。另外,對(duì)系統(tǒng)主要的外圍電路,如電源、復(fù)位等也需要仔細(xì)的考慮,在一些高速設(shè)計(jì)或特殊應(yīng)用場(chǎng)合,還需要考慮EMC/EMI等。

電源是保證硬件系統(tǒng)正常工作的基礎(chǔ),設(shè)計(jì)中要詳細(xì)的分析:系統(tǒng)能夠提供的電源輸入;單板需要產(chǎn)生的電源輸出;各個(gè)電源需要提供的電流大小;電源電路效率;各個(gè)電源能夠允許的波動(dòng)范圍;整個(gè)電源系統(tǒng)需要的上電順序等等。

為了系統(tǒng)穩(wěn)定可靠的工作,復(fù)位電路的設(shè)計(jì)也非常重要,如何保證系統(tǒng)不會(huì)在外界干擾的情況下異常復(fù)位,如何保證在系統(tǒng)運(yùn)行異常的時(shí)候能夠及時(shí)復(fù)位,以及如何合理的復(fù)位,才能保證系統(tǒng)完整的復(fù)位后,這些也都是我們?cè)谠碓O(shè)計(jì)的時(shí)候需要考慮的。

同樣的,時(shí)鐘電路的設(shè)計(jì)也是非常重要的一個(gè)方面,一個(gè)不好的時(shí)鐘電路設(shè)計(jì),可能會(huì)引起通信產(chǎn)品的數(shù)據(jù)丟包,產(chǎn)生大的EMI,甚至導(dǎo)致系統(tǒng)不穩(wěn)定。

原理圖設(shè)計(jì)中要有“拿來主義”!現(xiàn)在的芯片廠家一般都可以提供參考設(shè)計(jì)的原理圖,所以要盡量的借助這些資源,在充分理解參考設(shè)計(jì)的基礎(chǔ)上,做一些自己的發(fā)揮。

硬件階段4:PCB圖設(shè)計(jì)

PCB設(shè)計(jì)階段,即是將原理圖設(shè)計(jì)轉(zhuǎn)化為實(shí)際的可加工的PCB 線路板,目前主流的PCB 設(shè)計(jì)軟件有PADS,Candence 和Protel幾種。

PCB設(shè)計(jì),尤其是高速PCB,需要考慮EMC/EMI,阻抗控制,信號(hào)質(zhì)量等,對(duì)PCB 設(shè)計(jì)人員的要求比較高。為了驗(yàn)證設(shè)計(jì)的PCB是否符合要求,有的還需要進(jìn)行PCB 仿真。并依據(jù)仿真結(jié)果調(diào)整PCB 的布局布線,完成整個(gè)的設(shè)計(jì)。

硬件階段5:PCB加工文件制作與PCB打樣

PCB繪制完成以后,在這一階段,我們需要生成加工廠可識(shí)別的加工文件,即常說的光繪文件,將其交給加工廠打樣PCB 空板。一般1~4層板可以在一周內(nèi)完成打樣。

硬件階段6:硬件產(chǎn)品的焊接與調(diào)試

在拿到加工廠打樣會(huì)的 PCB空板以后,接下來我們,需要檢查PCB空板是否和我們?cè)O(shè)計(jì)預(yù)期一樣,是否存在明顯的短路或斷痕,檢查通過后,則需要將前期采購(gòu)的元器件和PCB空板交由生產(chǎn)廠家進(jìn)行焊接(如果PCB 電路不復(fù)雜,為了加快速度,也可以直接手工焊接元器件)。

當(dāng)PCB 已經(jīng)焊接完成后,在調(diào)試PCB之前,一定要先認(rèn)真檢查是否有可見的短路和管腳搭錫等故障,檢查是否有元器件型號(hào)放置錯(cuò)誤,第一腳放置錯(cuò)誤,漏裝配等問題,然后用萬(wàn)用表測(cè)量各個(gè)電源到地的電阻,以檢查是否有短路,這樣可以避免貿(mào)然上電后損壞單板。調(diào)試的過程中要有平和的心態(tài),遇見問題是非常正常的,要做的就是多做比較和分析,逐步的排除可能的原因,直致最終調(diào)試成功。

在硬件調(diào)試過程中,需要經(jīng)常使用到的調(diào)試工具有萬(wàn)用表和示波器,邏輯分析儀等,用于測(cè)試和觀察板內(nèi)信號(hào)電壓和信號(hào)質(zhì)量,信號(hào)時(shí)序是否滿足要求。

硬件階段7:硬件產(chǎn)品測(cè)試

當(dāng)硬件產(chǎn)品調(diào)試通過以后,我們需要對(duì)照產(chǎn)品產(chǎn)品的需求說明,一項(xiàng)一項(xiàng)進(jìn)行測(cè)試,確認(rèn)是否符合預(yù)期的要求,如果達(dá)不到要求,則需要對(duì)硬件產(chǎn)品進(jìn)行調(diào)試和修改,直到符合產(chǎn)品需求文明(一般都以需求說明文檔作為評(píng)判的一句,當(dāng)然明顯的需求說明錯(cuò)誤除外)。

硬件階段8:硬件產(chǎn)品

我們最終開發(fā)的硬件成功。一個(gè)完整的,完成符合產(chǎn)品需求的硬件產(chǎn)品還不能說明一個(gè)成功的產(chǎn)品開發(fā)過程,我們還需要按照預(yù)定計(jì)劃,準(zhǔn)時(shí)高質(zhì)量的完成。才是一個(gè)成功的產(chǎn)品開發(fā)過程。

嵌入式編程專輯 Linux 學(xué)習(xí)專輯 C/C++編程專輯 Qt進(jìn)階學(xué)習(xí)專輯 關(guān)注微信公眾號(hào)『技術(shù)讓夢(mèng)想更偉大』,后臺(tái)回復(fù)“m”查看更多內(nèi)容。 長(zhǎng)按前往圖中包含的公眾號(hào)關(guān)注