計(jì)算機(jī)體系架構(gòu)未來(lái)趨勢(shì)(深度)

將成為未來(lái)十年甚至更長(zhǎng)時(shí)間,計(jì)算機(jī)體系結(jié)構(gòu)的趨勢(shì)。登納德縮放定律結(jié)束、摩爾定律衰退,而阿姆達(dá)爾定律正當(dāng)其時(shí),這意味著低效性將每年的性能改進(jìn)限制在幾個(gè)百分點(diǎn)。獲得更高的性能改進(jìn)需要新的架構(gòu)方法,就是DSA。

計(jì)算機(jī)架構(gòu)的第二個(gè)機(jī)會(huì)是開(kāi)放的 ISA(Instruction Set Architecture,指令集合架構(gòu)),要?jiǎng)?chuàng)建處理器領(lǐng)域的Linux。

這讓我想起了2021年7月27日OCP China Day的第二演播廳(詳見(jiàn)視頻:數(shù)據(jù)處理怎么能變更快?),接受IT大嘴巴(劉策)的采訪時(shí),因西部數(shù)據(jù)Bill 劉總的啟發(fā),得出:開(kāi)放計(jì)算未來(lái)十年,除了在系統(tǒng)級(jí)(整機(jī)柜、機(jī)架服務(wù)器、邊緣服務(wù)器等),組件級(jí)(OAI、NVMe SSD、NIC 3.0、DPU等),還將在芯片級(jí)(如RISC-V、英偉達(dá)NVDLA)大有作為。

借助電子計(jì)算機(jī)輔助設(shè)計(jì)(ECAD)工具,使得敏捷開(kāi)發(fā)成為可能;這種更高水平的抽象增加了設(shè)計(jì)的重用性。從設(shè)計(jì)交付到返回芯片原來(lái)需要幾個(gè)月時(shí)間,現(xiàn)在可能四周左右。

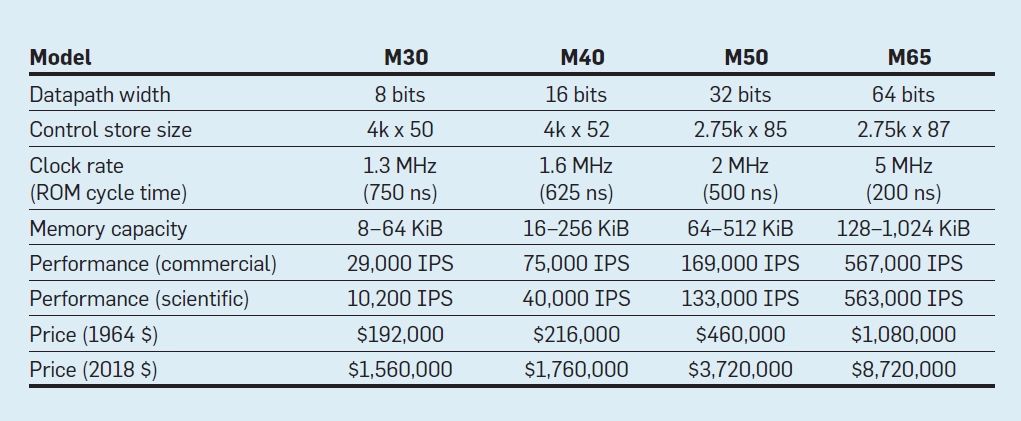

摩爾(Gordon Moore)在 1965 年的最初預(yù)測(cè)中,稱晶體管密度會(huì)每年翻一番;1975 年,他又預(yù)計(jì)每?jī)赡攴环?/span>

羅伯特·登納德(Robert Dennard)預(yù)測(cè)隨著晶體管密度的增加,每個(gè)晶體管的能耗將降低,因此硅芯片上每平方毫米上的能耗幾乎保持恒定。由于每平方毫米硅芯片的計(jì)算能力隨著技術(shù)的迭代而不斷增強(qiáng),計(jì)算機(jī)將變得更加節(jié)能。然而,登納德縮放定律從 2007 年開(kāi)始大幅放緩,2012 年左右接近失效(見(jiàn)圖 3)。

1986 年至 2002 年間,指令級(jí)并行(ILP)是提高性能的主要架構(gòu)方法。而且隨著晶體管速度的提高,其性能每年能提高 50% 左右。登納德縮放定律的終結(jié)意味著工程師必須找到更加高效的并行化利用方法。

為了保持工作流程完整,需要預(yù)測(cè)分支,并根據(jù)推測(cè)將代碼放入工作流程中以便執(zhí)行。推測(cè)的使用是 ILP 高性能和芯片低能效的源頭所在。如果分支預(yù)測(cè)完美,推測(cè)就能提高 ILP 性能,但能耗會(huì)增加一些——甚至可能節(jié)約能耗——但如果分支預(yù)測(cè)出現(xiàn)失誤,處理器就必須拋棄錯(cuò)誤的推測(cè)指令,其計(jì)算工作及所耗能量就會(huì)付之東流。處理器的內(nèi)部狀態(tài)也必須恢復(fù)到錯(cuò)誤預(yù)測(cè)分支之前的狀態(tài),這將花費(fèi)額外的時(shí)間和能量。

很少有通用程序能夠如此準(zhǔn)確地預(yù)測(cè)分支。架構(gòu)師需要一種不同的方法來(lái)實(shí)現(xiàn)性能改進(jìn)。于是多核時(shí)代就這樣誕生了。

多核將識(shí)別并行性和決定如何利用并行性的責(zé)任轉(zhuǎn)移給程序員和語(yǔ)言系統(tǒng)。多核并不能解決由登納德縮放定律終結(jié)帶來(lái)的能效計(jì)算挑戰(zhàn)。每個(gè)活躍的核都會(huì)消耗能量,無(wú)論其對(duì)計(jì)算是否具有有效貢獻(xiàn)。一個(gè)主要的障礙可以用阿姆達(dá)爾定律(Amdahl\'s Law)表述。

IBM360系列機(jī)的主要設(shè)計(jì)者阿姆達(dá)爾于1967年提出。

該定律指出:系統(tǒng)中對(duì)某一部件采用更快執(zhí)行方式所能獲得的系統(tǒng)性能改進(jìn)程度,取決于這種執(zhí)行方式被使用的頻率,或所占總執(zhí)行時(shí)間的比例。阿姆達(dá)爾定律實(shí)際上定義了采取增強(qiáng)(加速)某部分功能處理的措施后可獲得的性能改進(jìn)或執(zhí)行時(shí)間的加速比。簡(jiǎn)單來(lái)說(shuō)是通過(guò)更快的處理器來(lái)獲得加速是由慢的系統(tǒng)組件所限制。

阿姆達(dá)爾曾致力于并行處理系統(tǒng)的研究。對(duì)于固定負(fù)載情況下描述并行處理效果的加速比s,阿姆達(dá)爾經(jīng)過(guò)深入研究給出了如下公式:S=1/(1-a+a/n)

其中,a為并行計(jì)算部分所占比例,n為并行處理結(jié)點(diǎn)個(gè)數(shù)。這樣,當(dāng)1-a=0時(shí),(即沒(méi)有串行,只有并行)最大加速比s=n;當(dāng)a=0時(shí)(即只有串行,沒(méi)有并行),最小加速比s=1;當(dāng)n→∞時(shí),極限加速比s→ 1/(1-a),這也就是加速比的上限。例如,若串行代碼占整個(gè)代碼的25%,則并行處理的總體性能不可能超過(guò)4。

言歸正傳,下面是《計(jì)算機(jī)架構(gòu)的新黃金時(shí)代,兩位圖靈獎(jiǎng)得主最新力作》全文。

John Hennessy 和 David Patterson 是 2017 年圖靈獎(jiǎng)獲得者,目前這兩位學(xué)者都供職于谷歌,前者是谷歌母公司 Alphabet 的董事會(huì)主席,后者任谷歌杰出工程師,致力于研究機(jī)器學(xué)習(xí)和人工智能。他們更為人所知的就是共同完成的計(jì)算機(jī)系統(tǒng)結(jié)構(gòu)學(xué)科「圣經(jīng)」《計(jì)算機(jī)體系結(jié)構(gòu):量化研究方法》了。

本文《計(jì)算機(jī)架構(gòu)的新黃金時(shí)代》是兩人在 2019 年新發(fā)表的文章,完整介紹了計(jì)算機(jī)芯片的發(fā)展歷程,以及所有架構(gòu)的未來(lái)趨勢(shì),值得所有希望了解硬件架構(gòu)的人閱讀。

2018 年 6 月 4 日,我們回顧了自 20 世紀(jì) 60 年代以來(lái)計(jì)算機(jī)架構(gòu)的發(fā)展,并以此開(kāi)始了我們的圖靈講座(Turing Lecture)。除了那個(gè)回顧,我們還在講座中介紹了當(dāng)前的難題和未來(lái)機(jī)遇。我們還預(yù)測(cè)未來(lái)十年計(jì)算機(jī)架構(gòu)領(lǐng)域?qū)⒂瓉?lái)下一個(gè)黃金時(shí)代,就像 20 世紀(jì) 80 年代那樣——我們做的研究能為我們帶來(lái)回報(bào),能改善成本、能源、安全以及性能。

「不能銘記過(guò)去的人注定要重蹈覆轍。」 ——George Santayana,1905

軟件與硬件的通信是通過(guò)指令集架構(gòu)(ISA)進(jìn)行的。在 1960 年代早期,IBM 有四個(gè)互不兼容的計(jì)算機(jī)產(chǎn)品線,每個(gè)都有自己的 ISA、軟件堆棧、I/O 系統(tǒng)和利基市場(chǎng)(分別針對(duì)的是小型企業(yè)、大型企業(yè)、科研和實(shí)時(shí)應(yīng)用)。包括 ACM 圖靈獎(jiǎng)獲得者 Fred Brooks, Jr. 在內(nèi)的 IBM 工程師都認(rèn)為他們可以創(chuàng)造一種能有效統(tǒng)一所有這四種 ISA 基礎(chǔ)的單個(gè) ISA。

?

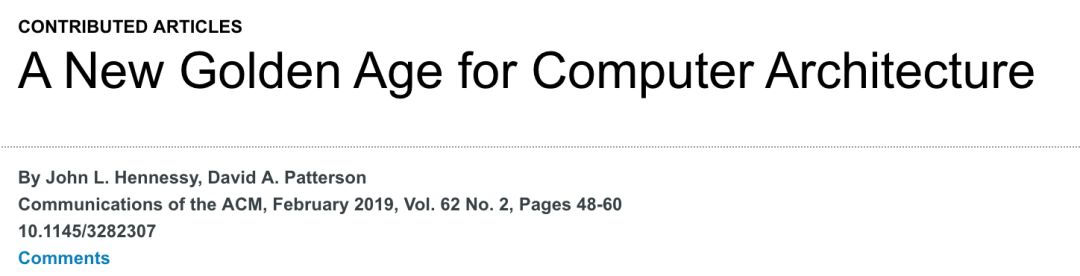

他們需要一種技術(shù)解決方案,讓便宜的 8 位數(shù)據(jù)路徑計(jì)算機(jī)與高速的 64 位數(shù)據(jù)路徑計(jì)算機(jī)都能共用一個(gè) ISA。這些數(shù)據(jù)路徑是處理器的「身體」,它們?cè)谄渲袌?zhí)行算術(shù)運(yùn)算但相對(duì)而言較容易「變寬」或「變窄」。對(duì)于那時(shí)以及現(xiàn)在的計(jì)算機(jī)設(shè)計(jì)者來(lái)說(shuō),最大的難題是處理器的「大腦」——控制硬件。受軟件編程的啟發(fā),計(jì)算先驅(qū)和圖靈獎(jiǎng)獲得者 Maurice Wilkes 提出了簡(jiǎn)化控制的方法。控制可被描述為一個(gè)二維數(shù)組,他稱之為「控制存儲(chǔ)器(control store)」。這個(gè)數(shù)組的每一列都對(duì)應(yīng)于一條控制線,每一行都是一個(gè)微指令(microinstruction),而編寫(xiě)微指令則被稱為微編程(microprogramming)。一個(gè)控制存儲(chǔ)器包含一個(gè)用微指令編寫(xiě)的 ISA 解釋器,所以執(zhí)行一個(gè)常規(guī)指令需要多個(gè)微指令。這種控制存儲(chǔ)器是通過(guò)內(nèi)存實(shí)現(xiàn)的,成本比邏輯門(mén)要低得多。

表 1 列出了 IBM 在 1964 年 4 月 7 日宣布的新 System/360 ISA 的 4 種型號(hào)。數(shù)據(jù)路徑的變化范圍有 8 倍,內(nèi)存容量的變化范圍有 16 倍,時(shí)鐘頻率是 4 倍,性能是 50 倍,成本接近 6 倍。成本最高的計(jì)算機(jī)的控制存儲(chǔ)器最寬,因?yàn)楦鼜?fù)雜的數(shù)據(jù)路徑使用更多控制線。成本最低的計(jì)算機(jī)因?yàn)橛布?jiǎn)單而有更窄的控制存儲(chǔ)器,但因?yàn)樗鼈冃枰鄷r(shí)鐘周期來(lái)執(zhí)行一個(gè) System/360 指令,所以需要更多微指令。

在微編程的推動(dòng)下,IBM 將公司的未來(lái)押在了這款新 ISA 上,寄希望其能革新計(jì)算行業(yè),為 IBM 贏得回報(bào)。IBM 成功主宰了這一市場(chǎng),IBM 計(jì)算機(jī)家族的大型機(jī)后裔在推出?55 年后仍然每年創(chuàng)造著 100 億美元的收入。

正如我們反復(fù)看到的那樣,盡管市場(chǎng)并不能完美地判定各種技術(shù)問(wèn)題,但鑒于架構(gòu)和商業(yè)計(jì)算機(jī)之間聯(lián)系緊密,市場(chǎng)才能最終決定架構(gòu)創(chuàng)新是否成功,而這往往需要大量的工程開(kāi)發(fā)投入。

當(dāng)計(jì)算機(jī)開(kāi)始使用集成電路時(shí),摩爾定律意味著控制存儲(chǔ)器可以變大很多。更大的內(nèi)存反過(guò)來(lái)又意味著允許使用更復(fù)雜的 ISA。要知道,數(shù)字設(shè)備公司(Digital Equipment Corp.)在 1977 年推出的 VAX-11/780 的控制存儲(chǔ)器為 5120 字×96 位,而其前一代僅有 256 字× 56 位。

某些制造商選擇開(kāi)放微編程功能,讓選定的客戶能添加定制功能,他們稱之為「可寫(xiě)控制存儲(chǔ)器(WCS)」。最有名的 WCS 計(jì)算機(jī)是 Alto,這是圖靈獎(jiǎng)得主 Chuck Thacker 和 Butler Lampson 及其同事于 1973 年一起為施樂(lè)(Xerox)帕洛阿托研究中心開(kāi)發(fā)的。這實(shí)際上是第一款個(gè)人計(jì)算機(jī)(PC),配備有首款位映像顯示器(bit-mapped display)和首個(gè)以太網(wǎng)局域網(wǎng)。用于這種全新顯示器和網(wǎng)絡(luò)的設(shè)備控制器是存儲(chǔ)在一個(gè) 4096 字×32 位 WCS 中的微程序。

1970 年代的微處理器(比如英特爾的 8080)仍處于 8 位時(shí)代,主要依靠匯編語(yǔ)言編寫(xiě)程序。互相競(jìng)爭(zhēng)的設(shè)計(jì)者會(huì)通過(guò)添加新的指令來(lái)趕超彼此,他們會(huì)通過(guò)匯編語(yǔ)言示例來(lái)展示自己的優(yōu)勢(shì)。

戈登·摩爾(Gordon Moore)相信英特爾的下一代 ISA 將會(huì)伴隨英特爾的一生,因此他聘用了很多聰明的計(jì)算機(jī)科學(xué)博士,并將他們送到波特蘭去發(fā)明出色的下一代 ISA。英特爾最早命名為 8800 的計(jì)算機(jī)架構(gòu)項(xiàng)目雄心勃勃——對(duì)任何時(shí)代而言都是如此,顯然也是 1980 年代最有野心的。它有基于 32 位的尋址能力、面向?qū)ο蟮募軜?gòu)、位長(zhǎng)可變的指令以及用時(shí)新的編程語(yǔ)言 Ada 編寫(xiě)的自己的操作傳統(tǒng)。

可惜這個(gè)雄心勃勃的項(xiàng)目晚了幾年,迫使英特爾在圣克拉拉開(kāi)始了一項(xiàng)緊急替換工作,在 1979 年推出了一款 16 位微處理器。英特爾給了新團(tuán)隊(duì) 52 周時(shí)間來(lái)開(kāi)發(fā)新的「8086」ISA 以及設(shè)計(jì)和構(gòu)建芯片。鑒于日程緊迫,這個(gè)團(tuán)隊(duì)實(shí)際上是把 8080 的 8 位寄存器和指令集擴(kuò)展成了 16 位,最后只用 10 人次的 3 個(gè)常規(guī)工作周完成了這款 ISA 的設(shè)計(jì)。這個(gè)團(tuán)隊(duì)按時(shí)完成了 8086 的開(kāi)發(fā),但在發(fā)布時(shí)卻沒(méi)引起什么關(guān)注。

英特爾非常幸運(yùn),IBM 當(dāng)時(shí)正在開(kāi)發(fā)一款個(gè)人計(jì)算機(jī)來(lái)與 Apple II 競(jìng)爭(zhēng),并需要一款 16 位微處理器。IBM 之前感興趣的是 Motorola 68000,其 ISA 與 IBM 360 類似,但卻落后于 IBM 激進(jìn)的計(jì)劃。IBM 轉(zhuǎn)而使用 8086 的 8 位總線版本。IBM 在 1981 年 8 月 12 日推出了這款 PC,希望到 1986 年時(shí)能售出 25 萬(wàn)臺(tái)。而實(shí)際上該公司在全球售出了 1 億臺(tái),為這款緊急代換的英特爾 ISA 鋪墊了一個(gè)非常光明的未來(lái)。

英特爾原本的 8800 項(xiàng)目更名了為 iAPX-432,并最終在 1981 年推出,但它需要多塊芯片并且存在嚴(yán)重的性能問(wèn)題。該項(xiàng)目在 1986 年終止,這一年,英特爾在 80386 中對(duì) 16 位 8086 ISA 進(jìn)行了擴(kuò)展,將其寄存器從 16 位擴(kuò)展到了 32 位。因此,摩爾的預(yù)測(cè)就是正確的了——下一代 ISA 確實(shí)會(huì)和英特爾一樣長(zhǎng)壽,但市場(chǎng)選擇了緊急代換的 8086,而不是專門(mén)精心開(kāi)發(fā)的 432。正如 Motorola 68000 和 iAPX-432 兩者的設(shè)計(jì)師都學(xué)到的那樣:市場(chǎng)往往缺乏耐心。

1980 年代早期,人們對(duì)更大型控制存儲(chǔ)器中大型微程序使用的復(fù)雜指令集計(jì)算機(jī)(CISC)進(jìn)行了一些研究。Unix 表明即使操作系統(tǒng)也可以使用高級(jí)語(yǔ)言編寫(xiě),關(guān)鍵問(wèn)題隨之變成了「編譯器會(huì)生成什么指令?」,而不是「編程者會(huì)使用什么匯編語(yǔ)言?」。硬件/軟件接口的顯著改進(jìn)為架構(gòu)創(chuàng)新帶來(lái)了機(jī)會(huì)。

圖靈獎(jiǎng)得主 John Cocke 與其同事為小型計(jì)算機(jī)開(kāi)發(fā)了更簡(jiǎn)單的 ISA 和編譯器。作為實(shí)驗(yàn),他們將自己研究的編譯器的目標(biāo)重新設(shè)定為:僅使用 IBM 360 ISA 中簡(jiǎn)單的 register-register 操作和 load-store 數(shù)據(jù)傳輸,避免更復(fù)雜的指令。他們發(fā)現(xiàn)使用這個(gè)簡(jiǎn)單的子集時(shí),程序運(yùn)行速度可快達(dá)三倍。Emer 和 Clark 發(fā)現(xiàn) VAX 指令中 20% 的指令需要 60% 的微代碼(microcode),但僅占據(jù) 0.2% 的執(zhí)行時(shí)間。

David Patterson 把在 DEC 的一次學(xué)術(shù)休假投入到了研究減少 VAX 指令中的漏洞上。他認(rèn)為,如果微處理器制造商遵循更大型計(jì)算機(jī)的 CISC ISA 設(shè)計(jì),則它們需要一種修復(fù)微代碼漏洞的方法。他為此寫(xiě)了一篇論文,但期刊《Computer》卻拒絕接收。審稿人認(rèn)為,使用如此復(fù)雜以至于需要修補(bǔ)的 ISA 開(kāi)發(fā)微處理器是很糟糕的。這次拒稿讓人們質(zhì)疑 CISC ISA 在微處理器方面的價(jià)值。諷刺的是,現(xiàn)代 CISC 微處理器確實(shí)需要包含微代碼修復(fù)機(jī)制,但他被拒稿的主要結(jié)果是啟發(fā)他為微處理器開(kāi)發(fā)更簡(jiǎn)單的 ISA——精簡(jiǎn)指令集計(jì)算機(jī)(RISC)。

這些觀察和向高級(jí)語(yǔ)言的轉(zhuǎn)移為 CISC 向 RISC 的過(guò)渡帶來(lái)了機(jī)會(huì)。首先,RISC 指令是經(jīng)過(guò)簡(jiǎn)化的,因此無(wú)需微代碼解釋器。RISC 指令通常和微指令一樣簡(jiǎn)單,硬件可以直接執(zhí)行。第二,之前用于 CISC ISA 的微代碼解釋器的快速內(nèi)存被用作了 RISC 指令的緩存。(緩存是小而快的內(nèi)存,臨時(shí)緩沖近期執(zhí)行過(guò)的指令,因?yàn)檫@樣的指令很可能很快就要重新使用。)第三,基于 Gregory Chaitin 圖著色方案的寄存器分配器使編譯器可以更加容易地有效使用寄存器,這對(duì)這些 register-register ISA 是有利的。最后,摩爾定律意味著 1980 年代單塊芯片中已有足以包含完整 32 位數(shù)據(jù)路徑的晶體管以及相應(yīng)的指令和數(shù)據(jù)緩存。

在今天的后 PC 時(shí)代,x86 的出貨量從 2011 年的頂峰每年都會(huì)下降約 10%,而 RISC 處理器芯片出貨量已經(jīng)激增到了 200 億。

例如圖 1 展示了 RISC-I 和 MIPS 微處理器,它們分別由 UC 伯克利和斯坦福在 1982 與 1983 年開(kāi)發(fā),它們展示了 RISC 的優(yōu)勢(shì)。這些芯片最終都展示在了頂尖電路會(huì)議上,即 1984 年的 IEEE 國(guó)際固態(tài)電路會(huì)議。當(dāng)時(shí)是非常矚目的成果,因?yàn)椴死退固垢5囊恍┭芯可軜?gòu)建超越工業(yè)上能構(gòu)建的微處理器。

這些學(xué)術(shù)界做出的芯片激勵(lì)了許多公司構(gòu)建 RISC 微處理器,也是那之后 15 年內(nèi)最快的芯片。下面的公式解釋了處理器的性能:

Time/Program = Instructions / Program x (Clock cycles) / Instruction x Time / (Clock cycle)

DEC 工程師后來(lái)表明,更復(fù)雜的 CISC ISA 每個(gè)程序執(zhí)行的指令數(shù)是 RISC 每個(gè)程序的 75%(上式第一項(xiàng)),在使用類似的技術(shù)時(shí),CISC 執(zhí)行每個(gè)指令要多消耗 5 到 6 個(gè)時(shí)鐘周期(第二項(xiàng)),使得 RISC 微處理器的速度大約快了 3 倍。

這樣的公式在上世紀(jì) 80 年代的計(jì)算機(jī)架構(gòu)書(shū)中還沒(méi)有,后來(lái)我們?cè)?1989 年發(fā)表了《計(jì)算機(jī)體系架構(gòu):量化研究方法》一書(shū)。子標(biāo)題表明了該書(shū)的主題:使用測(cè)量方法和基準(zhǔn)進(jìn)行量化評(píng)估,而不是像從前那樣依靠架構(gòu)師的直覺(jué)與經(jīng)驗(yàn)。我們使用的量化方法也受到了圖靈獎(jiǎng)得主 Donald Knuth 關(guān)于算法的書(shū)的啟發(fā)。

下一個(gè) ISA 創(chuàng)新應(yīng)該是對(duì) RISC 和 CISC 的繼承。超長(zhǎng)指令字(VLIW)及其「表親」顯式并行指令計(jì)算機(jī)(EPIC)使用了寬指令,其中在每條指令中捆綁了多個(gè)獨(dú)立操作。VLIW 和 EPIC 的擁護(hù)者當(dāng)時(shí)認(rèn)為,單個(gè)指令如果可以指定六個(gè)獨(dú)立的操作(兩個(gè)數(shù)據(jù)傳輸、兩個(gè)整型操作和兩個(gè)浮點(diǎn)操作),并且編譯器技術(shù)可以有效地將操作分配到六個(gè)指令槽,則硬件可以變得更簡(jiǎn)單。與 RISC 方法一樣,VLIW 和 EPIC 將工作從硬件轉(zhuǎn)移到編譯器。

通過(guò)合作,英特爾和惠普公司設(shè)計(jì)了一款基于 EPIC 理念的 64 位處理器來(lái)取代 32 位 x86。英特爾和惠普公司對(duì)第一款 EPIC 處理器(Itanium)的期望很高,但實(shí)際情況與開(kāi)發(fā)商的早期聲明并不相符。雖然 EPIC 方法適用于高度結(jié)構(gòu)化的浮點(diǎn)程序,但它很難實(shí)現(xiàn)具有較少可預(yù)測(cè)的緩存丟失或較不可預(yù)測(cè)分支的整型程序的高性能。正如 Donald Knuth 后來(lái)指出:「Itanium 方法...... 原被認(rèn)為非常贊,直到事實(shí)證明所希望的編譯器基本上不可能寫(xiě)出來(lái)。」專家們注意到 Itanium 的延遲和表現(xiàn)不佳,并借鑒泰坦尼克號(hào)事件重新將其命名為「Itanic」。市場(chǎng)再次失去了耐心,導(dǎo)致 64 位版本的 x86 成為 32 位 x86 的繼承者,而不是 Itanium。

好消息是 VLIW 仍然適用于較窄范圍的應(yīng)用程序、小程序、更簡(jiǎn)單的分支和省略緩存,包括數(shù)字信號(hào)處理。

AMD 和英特爾使用了 500 人的設(shè)計(jì)團(tuán)隊(duì)和頂尖半導(dǎo)體技術(shù)來(lái)減少 x86 和 RISC 的性能差距。再次受到簡(jiǎn)單流水線 vs 復(fù)雜指令性能優(yōu)勢(shì)的啟發(fā),指令解碼器在運(yùn)行中將復(fù)雜的 x86 指令轉(zhuǎn)換為類似 RSIC 的內(nèi)部微指令。然后 AMD 和英特爾將 RISC 微指令的執(zhí)行流水線化。RISC 設(shè)計(jì)師關(guān)于性能分離指令、數(shù)據(jù)緩存、芯片二級(jí)緩存、深度流水線,以及同時(shí)獲取和執(zhí)行多個(gè)指令的任何想法,都可以用在 x86 的設(shè)計(jì)上。AMD 和英特爾在 2011 年 PC 時(shí)代的巔峰期出了大約 3 億 5 千萬(wàn)個(gè)微處理器。PC 行業(yè)的高產(chǎn)量和低利潤(rùn)同樣意味著比 RISC 計(jì)算機(jī)更低的價(jià)格。

鑒于每年全球銷售的數(shù)億臺(tái) PC,PC 軟件成為一個(gè)巨大的市場(chǎng)。雖然 Unix 市場(chǎng)的軟件提供商會(huì)為不同的商業(yè) RISC ISA-Alpha、HP-PA、MIPS、Power 和 SPARC 提供不同的軟件版本,但 PC 市場(chǎng)卻享有單一的 ISA,因此軟件開(kāi)發(fā)商提供了「收縮包裝」軟件,只與 x86 ISA 二進(jìn)制兼容。2000 年,更大的軟件基礎(chǔ)、類似的性能和更低的價(jià)格使 x86 在臺(tái)式機(jī)和小型服務(wù)器市場(chǎng)中占據(jù)主導(dǎo)地位。

蘋(píng)果公司在 2007 年幫助推動(dòng)了后 PC 時(shí)代。智能手機(jī)公司不再購(gòu)買(mǎi)微處理器,而是采用其他公司的設(shè)計(jì)(包括 ARM 的 RISC 處理器)構(gòu)建自己的芯片系統(tǒng)(SoC)。移動(dòng)設(shè)備設(shè)計(jì)人員對(duì)芯片面積和能效以及性能進(jìn)行評(píng)估,表明 CISC ISA 設(shè)計(jì)的不足之處。此外,物聯(lián)網(wǎng)的到來(lái)大大促進(jìn)了處理器的數(shù)量以及芯片尺寸、功率、成本和性能所需的權(quán)衡。這種趨勢(shì)增加了設(shè)計(jì)時(shí)間和成本的重要性,進(jìn)一步使 CISC 處理器處于不利地位。在今天的后 PC 時(shí)代,x86 出貨量自 2011 年達(dá)到峰值以來(lái)每年下降近 10%,而采用 RISC 處理器的芯片則飆升至 200 億。如今,99%的 32 位和 64 位處理器都是 RISC。

結(jié)束這一歷史回顧,我們可以說(shuō)市場(chǎng)已經(jīng)解決了 RISC-CISC 的爭(zhēng)論。CISC 贏得了 PC 時(shí)代的后期階段,但 RISC 正在后 PC 時(shí)代占據(jù)主導(dǎo)。幾十年來(lái),都沒(méi)有出現(xiàn)新的 CISC ISA。令我們驚訝的是,在推出 35 年后,今天對(duì)于通用處理器來(lái)說(shuō),最佳的 ISA 仍然是 RISC。

「如果一個(gè)問(wèn)題無(wú)解,那它可能都不成問(wèn)題,而是一個(gè)事實(shí);我們不需要解決,而是隨著時(shí)間的推移來(lái)處理。」—Shimon Peres

雖然前面的部分聚焦在指令集架構(gòu)(ISA)設(shè)計(jì)上,大部分計(jì)算機(jī)架構(gòu)師并不設(shè)計(jì)新的 ISA,而是在現(xiàn)有的實(shí)現(xiàn)技術(shù)中實(shí)現(xiàn)現(xiàn)有的 ISA。自 20 世紀(jì) 70 年代后期以來(lái),選擇的技術(shù)一直是基于金屬氧化物半導(dǎo)體(MOS)的集成電路,首先是 n 型金屬氧化物半導(dǎo)體(nMOS),然后是互補(bǔ)金屬氧化物半導(dǎo)體(CMOS)。摩爾的預(yù)測(cè)中捕捉到的 MOS 技術(shù)驚人的進(jìn)步率一直促使架構(gòu)師設(shè)計(jì)更積極的方法來(lái)為給定的 ISP 實(shí)現(xiàn)更好的性能。在 1965 年的最初預(yù)測(cè)中,摩爾稱晶體管密度會(huì)每年翻一番;1975 年,他又預(yù)計(jì)每?jī)赡攴环T擃A(yù)測(cè)最終被稱為摩爾定律。因?yàn)榫w管密度呈二次增長(zhǎng),而增長(zhǎng)率呈線性增長(zhǎng),架構(gòu)師使用更多晶體管來(lái)提高性能。

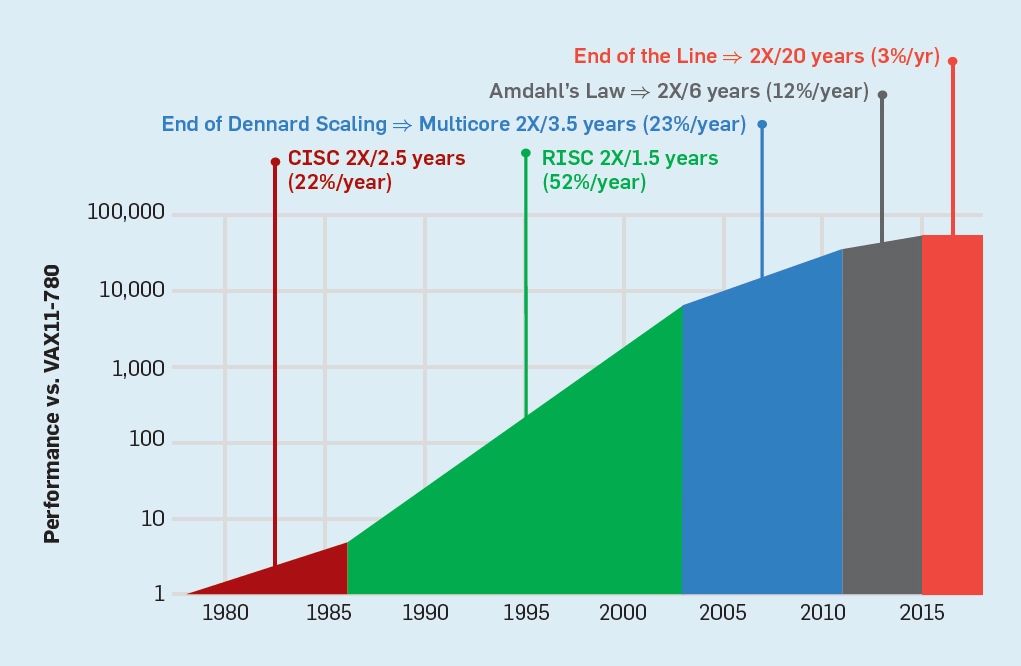

盡管摩爾定律已經(jīng)持續(xù)了幾十年(見(jiàn)圖 2),但在 2000 年左右開(kāi)始放緩。到了 2018 年,根據(jù)摩爾定律得出的預(yù)測(cè)與當(dāng)下實(shí)際能力差了 15 倍。根據(jù)當(dāng)前預(yù)測(cè),這一差距將持續(xù)拉大,因?yàn)?CMOS 技術(shù)方法已經(jīng)接近極限。

伴隨摩爾定律是由羅伯特·登納德(Robert Dennard)預(yù)測(cè)的登納德縮放定律(Dennard scaling)。他指出,隨著晶體管密度的增加,每個(gè)晶體管的能耗將降低,因此硅芯片上每平方毫米上的能耗幾乎保持恒定。由于每平方毫米硅芯片的計(jì)算能力隨著技術(shù)的迭代而不斷增強(qiáng),計(jì)算機(jī)將變得更加節(jié)能。登納德縮放定律從 2007 年開(kāi)始大幅放緩,2012 年左右接近失效(見(jiàn)圖 3)。

1986 年至 2002 年間,指令級(jí)并行(ILP)是提高性能的主要架構(gòu)方法。而且隨著晶體管速度的提高,其性能每年能提高 50% 左右。登納德縮放定律的終結(jié)意味著工程師必須找到更加高效的并行化利用方法。

要理解為什么 ILP 的增加會(huì)導(dǎo)致芯片能效大大降低,可以看一看 ARM、英特爾、AMD 當(dāng)前推出的處理器核。假設(shè)該芯片有一個(gè) 15 步的工作流程,每個(gè)時(shí)鐘周期可以發(fā)送 4 條指令。那么在任意一個(gè)時(shí)刻,整個(gè)工作流程中至多有 60 條指令,包括大約 15 個(gè)分支,因?yàn)樗鼈兇砹舜蠹s 25% 的執(zhí)行指令。為了保持工作流程完整,需要預(yù)測(cè)分支,并根據(jù)推測(cè)將代碼放入工作流程中以便執(zhí)行。推測(cè)的使用是 ILP 高性能和芯片低能效的源頭所在。如果分支預(yù)測(cè)完美,推測(cè)就能提高 ILP 性能,但能耗會(huì)增加一些——甚至可能節(jié)約能耗——但如果分支預(yù)測(cè)出現(xiàn)失誤,處理器就必須拋棄錯(cuò)誤的推測(cè)指令,其計(jì)算工作及所耗能量就會(huì)付之東流。處理器的內(nèi)部狀態(tài)也必須恢復(fù)到錯(cuò)誤預(yù)測(cè)分支之前的狀態(tài),這將花費(fèi)額外的時(shí)間和能量。

要理解這種設(shè)計(jì)的挑戰(zhàn)性有多高,可以考慮一下正確預(yù)測(cè) 15 個(gè)分支結(jié)果的難度。如果處理器要將做無(wú)用功的時(shí)間限制在 10%,那么它必須在 99.3% 的時(shí)間里正確預(yù)測(cè)每個(gè)分支。很少有通用程序能夠如此準(zhǔn)確地預(yù)測(cè)分支。

要理解這些無(wú)用功疊加起來(lái)是什么結(jié)果,可以參見(jiàn)圖 4 中的數(shù)據(jù)。圖 4 顯示了有效執(zhí)行的部分指令,這部分指令由于處理器推測(cè)錯(cuò)誤而變得無(wú)用。在英特爾酷睿 i7 基準(zhǔn)測(cè)試上,19% 的指令都被浪費(fèi)了,但能耗的浪費(fèi)情況更加嚴(yán)重,因?yàn)樘幚砥鞅仨毨妙~外的能量才能在推測(cè)失誤時(shí)恢復(fù)原來(lái)的狀態(tài)。這樣的度量導(dǎo)致許多人得出結(jié)論,架構(gòu)師需要一種不同的方法來(lái)實(shí)現(xiàn)性能改進(jìn)。于是多核時(shí)代就這樣誕生了。

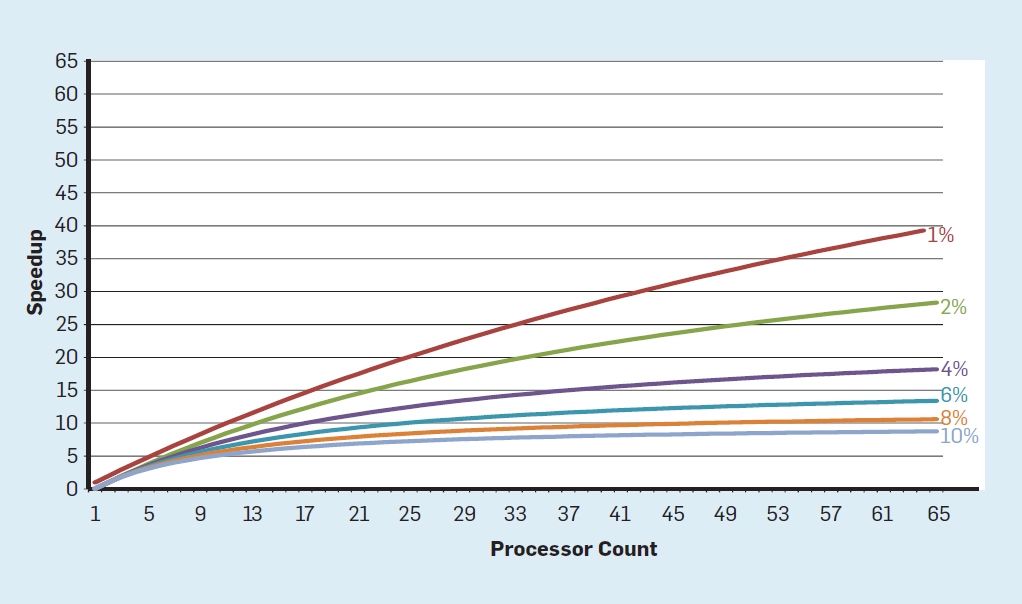

多核將識(shí)別并行性和決定如何利用并行性的責(zé)任轉(zhuǎn)移給程序員和語(yǔ)言系統(tǒng)。多核并不能解決由登納德縮放定律終結(jié)帶來(lái)的能效計(jì)算挑戰(zhàn)。每個(gè)活躍的核都會(huì)消耗能量,無(wú)論其對(duì)計(jì)算是否具有有效貢獻(xiàn)。一個(gè)主要的障礙可以用阿姆達(dá)爾定律(Amdahl\'s Law)表述,該定理認(rèn)為,并行計(jì)算機(jī)的加速受限于序列計(jì)算的部分。這一定律的重要性參見(jiàn)圖 5。圖中顯示,假設(shè)串行執(zhí)行的不同部分只有一個(gè)處理器處于活躍狀態(tài),那么與單個(gè)內(nèi)核相比,最多 64 個(gè)內(nèi)核的應(yīng)用程序運(yùn)行速度要快得多。例如,如果只有 1% 的時(shí)間是串行的,那么 64 核配置可加速大約 35 倍,所需能量與 64 個(gè)處理器成正比,因此大約有 45% 的能量被浪費(fèi)了。

備注:從上圖也可以看出,如果有 8% 的時(shí)間是串行的,那么 64 核配置僅可加速 10倍多一點(diǎn)。想詳細(xì)理解這部分可結(jié)合文章開(kāi)頭?阿姆達(dá)爾定律公式S=1/(1-a+a/n)?:1%的串行時(shí)間,意味著a=0.99;n是并行數(shù)

真實(shí)的程序結(jié)構(gòu)當(dāng)然會(huì)更加復(fù)雜,部分組件允許在給定時(shí)刻使用不同數(shù)量的處理器。然而,周期性通信和同步的需求意味著大部分應(yīng)用具備僅可高效使用一部分處理器的組件。盡管阿姆達(dá)爾定律已經(jīng)出現(xiàn) 50 多年了,它仍然是一個(gè)很大的障礙。

隨著登納德縮放定律的終結(jié),芯片內(nèi)核數(shù)量的增加意味著能耗也隨之增加。然而,進(jìn)入處理器的電能肯定有一部分會(huì)轉(zhuǎn)化為熱能。因此多核處理器受限于熱耗散功率(TDP),即封裝和冷卻系統(tǒng)可以移除的平均功率。盡管一些高端數(shù)據(jù)中心可能使用更先進(jìn)的封裝和冷卻技術(shù),但沒(méi)有一個(gè)計(jì)算機(jī)用戶想要在自己桌子上放置小型熱交換器,或者背著散熱器來(lái)冷卻手機(jī)。TDP 的局限性直接導(dǎo)致了「暗硅」(dark silicon)時(shí)代,處理器降低時(shí)鐘速率、關(guān)閉空閑內(nèi)核來(lái)防止過(guò)熱。這種方法的另一種解釋是:一些芯片可以重新分配其珍貴功耗,將其從空閑內(nèi)核轉(zhuǎn)移到活躍內(nèi)核。

登納德縮放定律結(jié)束、摩爾定律衰退,而阿姆達(dá)爾定律正當(dāng)其時(shí),這意味著低效性將每年的性能改進(jìn)限制在幾個(gè)百分點(diǎn)(見(jiàn)圖 6)。獲得更高的性能改進(jìn)(像 20 世紀(jì)八九十年代那樣)需要新的架構(gòu)方法,新方法應(yīng)能更加高效地利用集成電路。接下來(lái)我們將討論現(xiàn)代計(jì)算機(jī)的另一個(gè)主要缺陷——計(jì)算機(jī)安全問(wèn)題,之后我們會(huì)回來(lái)探討有效的新方法。

20 世紀(jì) 70 年代,處理器架構(gòu)師主要專注于計(jì)算機(jī)安全,涉及保護(hù)環(huán)、容量等概念。這些架構(gòu)師深刻了解到,大部分 bug 存在于軟件中,但他們認(rèn)為架構(gòu)支持會(huì)有所幫助。操作系統(tǒng)大部分未使用這些功能,操作系統(tǒng)專注于良性環(huán)境(如個(gè)人電腦),因此具備較大開(kāi)銷的功能未被使用。在軟件社區(qū)中,很多人認(rèn)為微內(nèi)核(microkernel)等正式驗(yàn)證技術(shù)會(huì)為構(gòu)建高度安全的軟件提供有效保障。但不幸的是,我們的軟件系統(tǒng)規(guī)模和性能驅(qū)動(dòng)器意味著此類技術(shù)無(wú)法跟上處理器性能。結(jié)果就是大型軟件系統(tǒng)仍然有很多安全漏洞,且由于海量在線個(gè)人信息和云計(jì)算的使用,其影響被放大。

登納德縮放定律的終結(jié)意味著架構(gòu)師必須找到利用并行化的更高效方式。

盡管計(jì)算機(jī)架構(gòu)師等很晚才意識(shí)到安全的重要性,但他們已經(jīng)開(kāi)始對(duì)虛擬機(jī)和加密提供硬件支持。不幸的是,推測(cè)給許多處理器帶來(lái)了一個(gè)未知但重要的安全缺陷。具體來(lái)看,Meltdown 和 Spectre 安全漏洞給微架構(gòu)帶來(lái)了新的缺陷,使受保護(hù)信息遭到泄露。這兩種漏洞都使用了旁路攻擊。2018 年,研究者展示了在攻擊者不將代碼加載到目標(biāo)處理器的情況下,如何利用 Spectre 變體導(dǎo)致網(wǎng)絡(luò)信息泄露。盡管這次名為 NetSpectre 的攻擊泄露信息速度較慢,但它使同一局域網(wǎng)中的所有機(jī)器都受到攻擊,這造成了很多新的難題。虛擬機(jī)架構(gòu)還有兩個(gè)漏洞。一個(gè)是 Foreshadow,會(huì)影響專門(mén)保護(hù)高風(fēng)險(xiǎn)數(shù)據(jù)(如加密密鑰)的英特爾 SGX 安全機(jī)制。每個(gè)月都會(huì)發(fā)現(xiàn)新的漏洞。

旁路攻擊并非新鮮事,但是在最早期的案例中,促使旁路攻擊成功的是軟件缺陷。而在 Meltdown、Spectre 等攻擊中,硬件實(shí)現(xiàn)中的缺陷導(dǎo)致受保護(hù)信息泄露。這是處理器架構(gòu)師定義什么是 ISA 正確實(shí)現(xiàn)的一個(gè)基本難題,因?yàn)闃?biāo)準(zhǔn)定義中并未提及執(zhí)行指令序列的性能影響,而僅僅涉及 ISA-visible 執(zhí)行架構(gòu)狀態(tài)。架構(gòu)師需要重新思考對(duì) ISA 正確實(shí)現(xiàn)的定義,以避免此類安全漏洞。同時(shí),他們還應(yīng)該重新思考對(duì)計(jì)算機(jī)安全的側(cè)重點(diǎn),以及架構(gòu)師如何與軟件設(shè)計(jì)師一道實(shí)現(xiàn)更加安全的系統(tǒng)。架構(gòu)師(以及每個(gè)人)都過(guò)于依賴信息系統(tǒng),以至于對(duì)安全的重視程度不如對(duì)一流設(shè)計(jì)的關(guān)注。

「我們的機(jī)遇就在那些『無(wú)解問(wèn)題』之中。」——John Gardner, 1965

通用處理器固有的低效性,以及登納德縮放定律和摩爾定律的終結(jié),使得處理器架構(gòu)師和設(shè)計(jì)師很可能無(wú)法維持通用處理器中的顯著性能改進(jìn)。鑒于改進(jìn)性能對(duì)新的軟件能力的重要性,我們必須問(wèn):有沒(méi)有其他的有效方法?

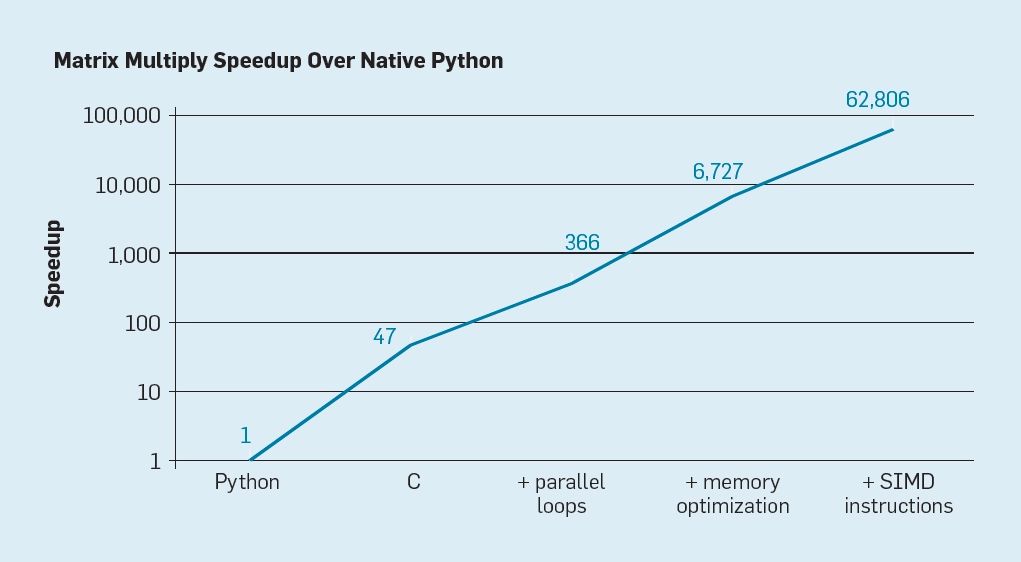

現(xiàn)在有兩個(gè)很明確的機(jī)會(huì),把二者結(jié)合起來(lái)則是第三個(gè)機(jī)會(huì)。首先,現(xiàn)有的軟件構(gòu)建技術(shù)廣泛使用具備動(dòng)態(tài)類型和存儲(chǔ)管理的高級(jí)語(yǔ)言。但是,此類語(yǔ)言的解釋和執(zhí)行通常非常低效。Leiserson 等人使用一個(gè)小例子(執(zhí)行矩陣相乘)說(shuō)明了這種低效性。如圖 7 所示,簡(jiǎn)單地將 Python 語(yǔ)言代碼重寫(xiě)為 C 代碼就可以將性能提升 46 倍(Python 是典型的高級(jí)、動(dòng)態(tài)類型語(yǔ)言)。

在多核上運(yùn)行并行循環(huán)(parallel loops)又將性能提升接近 7 倍。優(yōu)化內(nèi)存配置又將性能提升了近 19 倍,而通過(guò)單指令多數(shù)據(jù)(SIMD)并行化操作(一個(gè)指令執(zhí)行 16 個(gè) 32-bit 運(yùn)算)的硬件擴(kuò)展,性能又提升了 8 倍多。也就是說(shuō),最終的高度優(yōu)化版本在多核英特爾處理器上的運(yùn)行速度是初始 Python 版本的 62,000 多倍。這當(dāng)然只是一個(gè)很小的例子,但我們會(huì)期望程序員使用優(yōu)化庫(kù)。盡管這夸大了常見(jiàn)的性能差距,但很多程序的性能差距可能達(dá)到 100 到 1000 倍。

一個(gè)有趣的研究方向有關(guān)是否可以使用新的編譯器技術(shù)來(lái)縮短性能差距(可以輔以體系架構(gòu)增強(qiáng))。盡管高效編譯和實(shí)現(xiàn) Python 這樣的高級(jí)腳本語(yǔ)言比較困難,但潛在的收益是巨大的。即使實(shí)現(xiàn) 25% 的提升潛力,也能讓 Python 程序的運(yùn)行速度提升百倍。這個(gè)簡(jiǎn)單的例子展示了現(xiàn)代語(yǔ)言中,程序員強(qiáng)調(diào)生產(chǎn)力和傳統(tǒng)方法強(qiáng)調(diào)性能之間的巨大差距。

特定領(lǐng)域的體系結(jié)構(gòu)(備注:Domain-specific architectures,縮寫(xiě)為DSA)。

一種更加以硬件為中心的設(shè)計(jì)思路是設(shè)計(jì)針對(duì)特定問(wèn)題和領(lǐng)域的架構(gòu),并給與它們強(qiáng)大(且高效)的性能,因此它們是「特定領(lǐng)域的體系結(jié)構(gòu)(DSA)」,這是一種特定領(lǐng)域的可編程處理器,通常是圖靈完備的,但針對(duì)特定類別的應(yīng)用進(jìn)行了定制。從這個(gè)意義上來(lái)說(shuō),它們與專用集成電路(ASIC)不同,后者僅適用于單一功能,代碼很少有變化。DSA 通常被稱為加速器,因?yàn)榕c在通用 CPU 上執(zhí)行整個(gè)應(yīng)用程序相比,它們可以加速某些應(yīng)用程序。此外,DSA 可以實(shí)現(xiàn)更好的性能,因?yàn)樗鼈兏N近應(yīng)用的實(shí)際需求;DSA 的例子包括圖形加速單元(即?GPU),用于深度學(xué)習(xí)的神經(jīng)網(wǎng)絡(luò)處理器,以及軟件定義處理器(SDN)。DSA 效率更高,能耗更低是因?yàn)橐韵滤膫€(gè)原因:

第一,DSA 為特定領(lǐng)域的計(jì)算使用了更加有效的并行形式。例如單指令多數(shù)據(jù)并行(SIMD)比多指令多數(shù)據(jù)(MIMD)更有效,因?yàn)樗谝粋€(gè)時(shí)鐘步長(zhǎng)內(nèi)只需處理一個(gè)指令流和處理單元。盡管 SIMD 相比 MIMD 沒(méi)那么靈活,但前者適用于很多 DSA。DSA 也可以使用 VLIW 方法來(lái)實(shí)現(xiàn) ILP,而不是推測(cè)性的無(wú)序機(jī)制。如前文所述,VLIW 處理器與通用性代碼不匹配,但對(duì)于有限領(lǐng)域更加有效,因?yàn)樗目刂茩C(jī)制更加簡(jiǎn)單。特別是大多數(shù)高端通用處理器都是超標(biāo)量的,需要復(fù)雜的控制邏輯來(lái)啟動(dòng)和完成指令。與之相對(duì)的是,VLIW 在編譯時(shí)執(zhí)行必要的分析和調(diào)度,這對(duì)于顯式并行程序來(lái)說(shuō)可以很好地工作。

第二,DSA 可以更有效地利用內(nèi)存層次結(jié)構(gòu)。如 Horowitz 所述,內(nèi)存訪問(wèn)要比算數(shù)計(jì)算的成本高出很多。例如,訪問(wèn) 32 千字節(jié)緩存需要的能量相當(dāng)于做 32 位加法的大約 200 倍。這種巨大的差異使得優(yōu)化存儲(chǔ)器訪問(wèn)對(duì)于實(shí)現(xiàn)高能效來(lái)說(shuō)至關(guān)重要。通用處理器的運(yùn)行代碼,其中的存儲(chǔ)器訪問(wèn)通常表現(xiàn)出空間和時(shí)間局部性,但在編譯時(shí)不是非常可預(yù)測(cè)的。因此,CPU 使用多級(jí)高速緩存來(lái)增加帶寬,并隱藏相對(duì)較慢的芯片外 DRAM 延遲。這些多級(jí)高速緩存通常消耗大約一半的處理器能量,但幾乎忽略了所有片外 DRAM 訪問(wèn),這些訪問(wèn)需要大約 10 倍于最后一級(jí)高速緩存訪問(wèn)的能量。

緩存有兩大缺點(diǎn):

當(dāng)數(shù)據(jù)集非常大的時(shí)候,時(shí)間空間位置較低時(shí)緩存的工作效率很低; 當(dāng)緩存工作效率高的時(shí)候,位置非常高,這意味著同時(shí)根據(jù)定義,大多數(shù)緩存在大多數(shù)時(shí)間都處于空閑狀態(tài)。

在那些編譯時(shí)可以很好地定義和發(fā)現(xiàn)內(nèi)存訪問(wèn)模式的應(yīng)用程序中——這對(duì)于典型的 DSL(Domain-Specific Languages,特定領(lǐng)域的語(yǔ)言)來(lái)說(shuō)是常見(jiàn)的——程序員和編譯器可以比動(dòng)態(tài)分配的緩存更好地優(yōu)化內(nèi)存的使用。因此,DSA 通常使用由軟件明確控制運(yùn)動(dòng)的存儲(chǔ)器層次,類似于矢量處理器的操作。對(duì)于合適的應(yīng)用,用戶控制的存儲(chǔ)器可以比高速緩存使用更少的能量。

第三,DSA 在可接受時(shí)可以使用較低的精度。適用于通用任務(wù)的 CPU 通常支持 32 和 64 位整型數(shù)和浮點(diǎn)數(shù)數(shù)據(jù)。對(duì)于很多機(jī)器學(xué)習(xí)和圖像應(yīng)用來(lái)說(shuō),這種準(zhǔn)確率有點(diǎn)浪費(fèi)了。例如在深度神經(jīng)網(wǎng)絡(luò)中(DNN),推理通常使用 4、8 或 16 位整型數(shù),從而提高數(shù)據(jù)和計(jì)算吞吐量。同樣,對(duì)于 DNN 訓(xùn)練程序,浮點(diǎn)數(shù)很有意義,但 32 位就夠了,16 為經(jīng)常也能用。

最后,DSA 受益于以特定領(lǐng)域語(yǔ)言(DSL)編寫(xiě)的目標(biāo)程序,這些程序可以實(shí)現(xiàn)更高的并行性,更好的內(nèi)存結(jié)構(gòu)訪問(wèn)和表示,并使應(yīng)用程序更有效地映射到特定域的處理器。

DSA 要求將高級(jí)運(yùn)算定位到體系架構(gòu)中,但一般嘗試從 Python、Java、C 或 Fortran 等通用語(yǔ)言抽取結(jié)構(gòu)和信息實(shí)在太難了。因此特定領(lǐng)域的語(yǔ)言(DSL)特別支持這一過(guò)程,并盡可能高效地編程 DSA。例如?DSL 可以令向量、密集型矩陣和稀疏性矩陣運(yùn)算變得顯式化,并允許 DSL 編譯器高效地將運(yùn)算映射到處理器中。DSL 有很多常見(jiàn)的例子,例如專注矩陣運(yùn)算的語(yǔ)言 Matlab、專注 DNN 編程的數(shù)據(jù)流語(yǔ)言 TensorFlow,以及專注編程 SDN 的語(yǔ)言 P4 和專注圖像處理中高級(jí)轉(zhuǎn)換的 Halide 等。

使用 DSL 的挑戰(zhàn)是如何保證足夠的架構(gòu)獨(dú)立性,使得 DSL 中編寫(xiě)的的軟件可以移植到不同的架構(gòu),同時(shí)軟件映射到底層 DSA 的效率還要非常高。例如 XLA 系統(tǒng)將 TensorFLow 代碼轉(zhuǎn)化為能使用 GPU 或 TPU 等異構(gòu)處理器的計(jì)算圖。DSA 之間的平衡可移植性以及效率是編程語(yǔ)言設(shè)計(jì)者、編譯器設(shè)計(jì)者和 DSA 架構(gòu)師都感興趣的研究領(lǐng)域。

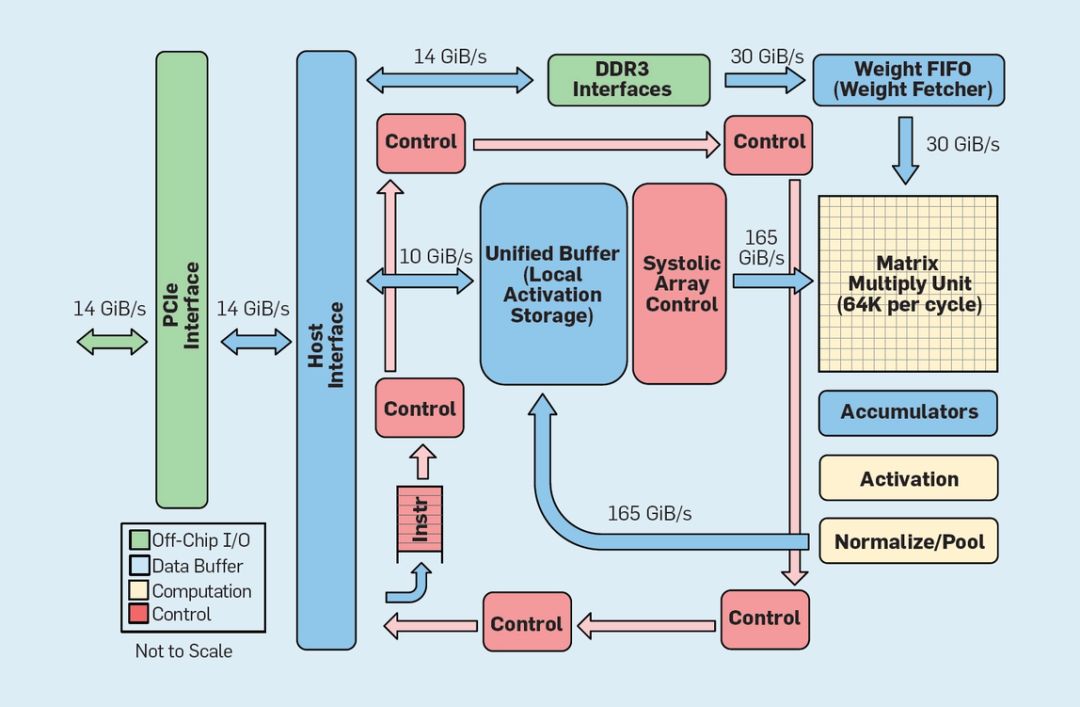

作為 DSA 的示例,我們可以考慮谷歌 TPU 1 的設(shè)計(jì),它旨在加速神經(jīng)網(wǎng)絡(luò)的推斷過(guò)程。TPU 自 2015 年投入生產(chǎn),它從搜索引擎到語(yǔ)言翻譯和圖像識(shí)別支持著谷歌各種各樣的業(yè)務(wù),同時(shí)也支持著 AlphaGo 和 AlphaZero 等 DeepMind 前沿研究。

TPU 的目標(biāo)是提升深度神經(jīng)網(wǎng)絡(luò)推斷過(guò)程的性能與能源效率 10 倍。

如下圖 8 所示,TPU 的組織架構(gòu)與通用處理器完全不同。它的主計(jì)算單元是矩陣單元,即每個(gè)時(shí)鐘周期提供提供 256×256 乘加運(yùn)算的脈動(dòng)陣列(systolic array)。TPU 還結(jié)合了 8-bit 精度、高效脈動(dòng)架構(gòu)(systolic structure)和 SIMD 控制特性,這意味著每個(gè)時(shí)鐘周期所能執(zhí)行的乘加(multiply-accumulates)數(shù)是一般通用單核 CPU 的 100 倍。

TPU 使用 24MB 的本地內(nèi)存以代替高速緩存,大約是 2015 年相同功耗 CPU 的兩倍。最后,激活值內(nèi)存和權(quán)重內(nèi)存(包括儲(chǔ)存權(quán)重的 FIFO 結(jié)構(gòu))可以通過(guò)用戶控制的高帶寬內(nèi)存通道連接。使用谷歌數(shù)據(jù)中心常見(jiàn)的 6 個(gè)推斷問(wèn)題的加權(quán)算術(shù)均值作為度量,TPU 比一般 CPU 要快 29 倍。因?yàn)?TPU 要求的能源少了一半,它的能源效率在這樣的工作負(fù)載中是一般 CPU 的 80 倍。

我們考慮了兩種不同的通過(guò)提升硬件技術(shù)效率來(lái)提升編程性能的方法:首先,通過(guò)提升現(xiàn)代高級(jí)語(yǔ)言的性能;其次,通過(guò)構(gòu)建領(lǐng)域特定的相比通用 CPU 能顯著提升性能和效率的架構(gòu)。DSL 是另一個(gè)如何改進(jìn)支持 DSA 等架構(gòu)創(chuàng)新的硬件/軟件接口的例子。要通過(guò)這些方法獲得顯著收益將需要一個(gè)垂直集成的設(shè)計(jì)團(tuán)隊(duì),該團(tuán)隊(duì)了解應(yīng)用程序、領(lǐng)域特定的語(yǔ)言和相關(guān)的編譯器技術(shù)、計(jì)算機(jī)體系結(jié)構(gòu)、組織以及底層實(shí)現(xiàn)技術(shù)。在行業(yè)橫向結(jié)構(gòu)化之前,需要在跨抽象層次上垂直集成并做出設(shè)計(jì)決策,這是計(jì)算機(jī)技術(shù)研發(fā)早期的主要特征。在這個(gè)新時(shí)代,垂直整合變得更加重要,能夠檢查和進(jìn)行復(fù)雜權(quán)衡以及優(yōu)化的團(tuán)隊(duì)將會(huì)受益。

GPU:英偉達(dá) GPU 使用了很多核心,每個(gè)核心都有大型寄存器文件、很多硬件線程和緩存; TPU:谷歌 TPU 依賴于大型二維收縮乘法器和板載內(nèi)存的硬件控制; FPGA:微軟在其數(shù)據(jù)中心里部署了現(xiàn)場(chǎng)可編程門(mén)陣列器件(FPGA),專用于神經(jīng)網(wǎng)絡(luò)應(yīng)用; CPU:英特爾提供通過(guò)大型高級(jí)緩存和一維 SIMD 指令增強(qiáng)的帶有很多核心的 CPU,微軟使用的 FPGA,以及一種新型的神經(jīng)網(wǎng)絡(luò)處理器,這種處理器相比 CPU 更加接近 TPU。

除了這些大企業(yè)外,還有數(shù)十家創(chuàng)業(yè)公司正在推行自己的方案。為了滿足不斷增長(zhǎng)的需求,架構(gòu)工程師正在將數(shù)百到數(shù)千個(gè)此類芯片互連以形成神經(jīng)網(wǎng)絡(luò)超級(jí)計(jì)算機(jī)。

DNN 架構(gòu)的雪崩式涌現(xiàn)使計(jì)算機(jī)架構(gòu)領(lǐng)域進(jìn)入了一個(gè)有趣的時(shí)代。在 2019 年很難預(yù)測(cè)這些方向中哪些(或者即使有)會(huì)贏,但市場(chǎng)肯定會(huì)像在解決過(guò)去的架構(gòu)爭(zhēng)論一樣解決競(jìng)爭(zhēng)問(wèn)題。

受開(kāi)源軟件成功的啟發(fā),計(jì)算機(jī)架構(gòu)的第二個(gè)機(jī)會(huì)是開(kāi)放的 ISA(Instruction Set Architecture,指令集合架構(gòu))。要?jiǎng)?chuàng)建處理器中的「Linux」,該領(lǐng)域需要行業(yè)標(biāo)準(zhǔn)的開(kāi)放式 ISA,除了擁有專利技術(shù)的個(gè)別公司以外,社區(qū)可以創(chuàng)建開(kāi)源核心。如果許多組織使用相同的 ISA 設(shè)計(jì)處理器,那么更大的競(jìng)爭(zhēng)可能會(huì)推動(dòng)更快的創(chuàng)新。目標(biāo)是為芯片提供處理器,成本從幾美分到 100 美元不等。

第一個(gè)例子是 RISC-V(稱為「RISC Five」),這是加州大學(xué)伯克利分校開(kāi)發(fā)的第五個(gè) RISC 架構(gòu)。RISC-V 有一個(gè)社區(qū),在 RISC-V 基金會(huì)的管理下維護(hù)架構(gòu)。開(kāi)放性允許 ISA 在公開(kāi)環(huán)境中演變,硬件和軟件專家在決策最終確定之前進(jìn)行協(xié)作。開(kāi)放式基金的另一個(gè)好處是 ISA 不太可能主要出于營(yíng)銷原因而擴(kuò)展,這有時(shí)是專有指令集擴(kuò)展的唯一原因。

RISC-V 是一個(gè)模塊化指令集。一小部分指令運(yùn)行完整的開(kāi)源軟件堆棧,然后是可選的標(biāo)準(zhǔn)擴(kuò)展,設(shè)計(jì)人員可以根據(jù)需要包含或省略。該基礎(chǔ)包括 32 位地址和 64 位地址版本。RISC-V 只能通過(guò)可選擴(kuò)展來(lái)增長(zhǎng);即使架構(gòu)師不接受新的擴(kuò)展,軟件堆棧仍然運(yùn)行良好。專有架構(gòu)通常需要向上的二進(jìn)制兼容性,這意味著當(dāng)處理器公司添加新功能時(shí),所有未來(lái)的處理器也必須包含它。對(duì)于 RISC-V,情況并非如此,所有增強(qiáng)功能都是可選的,如果應(yīng)用程序不需要,可以刪除。以下是目前為止的標(biāo)準(zhǔn)擴(kuò)展,使用代表其全名的縮寫(xiě):

M. 整型數(shù)乘法/除法; A. 原子內(nèi)存操作; F/D. 單/雙精度浮點(diǎn)數(shù); C. 壓縮指令。

更少指令。RISC-V 的指令少得多。base 中有 50 個(gè)指令,與原始 RISC-I 相近。剩余的標(biāo)準(zhǔn)擴(kuò)展(M、A、F 和 D)增加了 53 條指令,再加上 C 又增加了 34 條,共計(jì) 137 條。ARMv8 有超過(guò) 500 條指令。

更少的指令格式。RISC-V 的指令格式非常少,只有六種,而 ARMv8 至少有 14 種。

簡(jiǎn)單性減少了設(shè)計(jì)處理器和驗(yàn)證硬件正確性的工作量。由于 RISC-V 的目標(biāo)范圍覆蓋了數(shù)據(jù)中心芯片到物聯(lián)網(wǎng)設(shè)備,因此設(shè)計(jì)驗(yàn)證可能是開(kāi)發(fā)成本的重要組成部分。

RISC-V 是一種簡(jiǎn)潔的設(shè)計(jì),誕生 25 年后,它的設(shè)計(jì)師從其前輩的錯(cuò)誤中吸取了教訓(xùn)。與第一代 RISC 架構(gòu)不同,它避免了微架構(gòu)或技術(shù)依賴的功能(例如延遲分支和延遲加載)或創(chuàng)新(例如寄存器窗口),這些功能被編譯器技術(shù)的進(jìn)步所取代。

最后,RISC-V 通過(guò)為自定義加速器保留大量操作碼空間來(lái)支持 DSA。

安全專家不相信不可見(jiàn)的安全性,因此開(kāi)放式實(shí)現(xiàn)很有吸引力,開(kāi)放式實(shí)現(xiàn)需要開(kāi)放式架構(gòu)。

除 RISC-V 外,英偉達(dá) 2017 年還宣布一個(gè)免費(fèi)開(kāi)放的架構(gòu),稱之為英偉達(dá)深度學(xué)習(xí)加速器(NVDLA),這是一種可擴(kuò)展的可配置 DSA,用于機(jī)器學(xué)習(xí)推理。配置選項(xiàng)包括數(shù)據(jù)類型(int8、int16 或 fp16)和二維乘法矩陣的大小。模具尺寸從 0.5 mm^2 到 3 mm^2,功率從 20 毫瓦到 300 毫瓦。ISA、軟件堆棧和實(shí)現(xiàn)都是開(kāi)放的。

開(kāi)放的簡(jiǎn)單架構(gòu)與安全性具有協(xié)同作用。首先,安全專家不相信安全性,因此開(kāi)放式實(shí)現(xiàn)很有吸引力,而開(kāi)放式實(shí)現(xiàn)需要開(kāi)放式架構(gòu)。同樣重要的是增加可以圍繞安全架構(gòu)進(jìn)行創(chuàng)新的人員和組織的數(shù)量。專有架構(gòu)限制了員工的參與,但開(kāi)放式架構(gòu)允許學(xué)術(shù)界和工業(yè)界的所有最佳人才幫助提高安全性。最后,RISC-V 的簡(jiǎn)單性使其實(shí)現(xiàn)更容易檢查。此外,開(kāi)放式架構(gòu)、實(shí)現(xiàn)、軟件堆棧以及 FPGA 的可塑性意味著架構(gòu)師可以在線部署和評(píng)估新穎的解決方案,并每周而不是每年迭代它們。雖然 FPGA 比定制芯片慢 10 倍,但這種性能仍然足以支持在線用戶,同時(shí)帶來(lái)安全創(chuàng)新,解決真正的攻擊。我們希望開(kāi)放式架構(gòu)成為架構(gòu)師和安全專家進(jìn)行硬件/軟件協(xié)同設(shè)計(jì)的典范。

Beck 等人 2001 年提出的《敏捷軟件開(kāi)發(fā)宣言》(The Manifesto for Agile Software Development)徹底改變了軟件開(kāi)發(fā)方式,克服了瀑布式開(kāi)發(fā)中傳統(tǒng)精細(xì)規(guī)劃和文檔的頻繁失敗。小型編程團(tuán)隊(duì)很快開(kāi)發(fā)了有用但不完整的原型,并在進(jìn)行下一次迭代之前獲得了顧客的反饋。敏捷開(kāi)發(fā)的 scrum 版本集合了 5 到 10 名程序員組成的團(tuán)隊(duì),每次迭代進(jìn)行 2 到 4 周的沖刺。

再次受到軟件開(kāi)發(fā)成功的啟發(fā),第三次機(jī)會(huì)是敏捷硬件開(kāi)發(fā)。對(duì)架構(gòu)師來(lái)說(shuō)的一個(gè)好消息是,當(dāng)代電子計(jì)算機(jī)輔助設(shè)計(jì)(ECAD)工具提高了抽象水平,使得敏捷開(kāi)發(fā)成為可能,而且這種更高水平的抽象增加了設(shè)計(jì)的重用性。

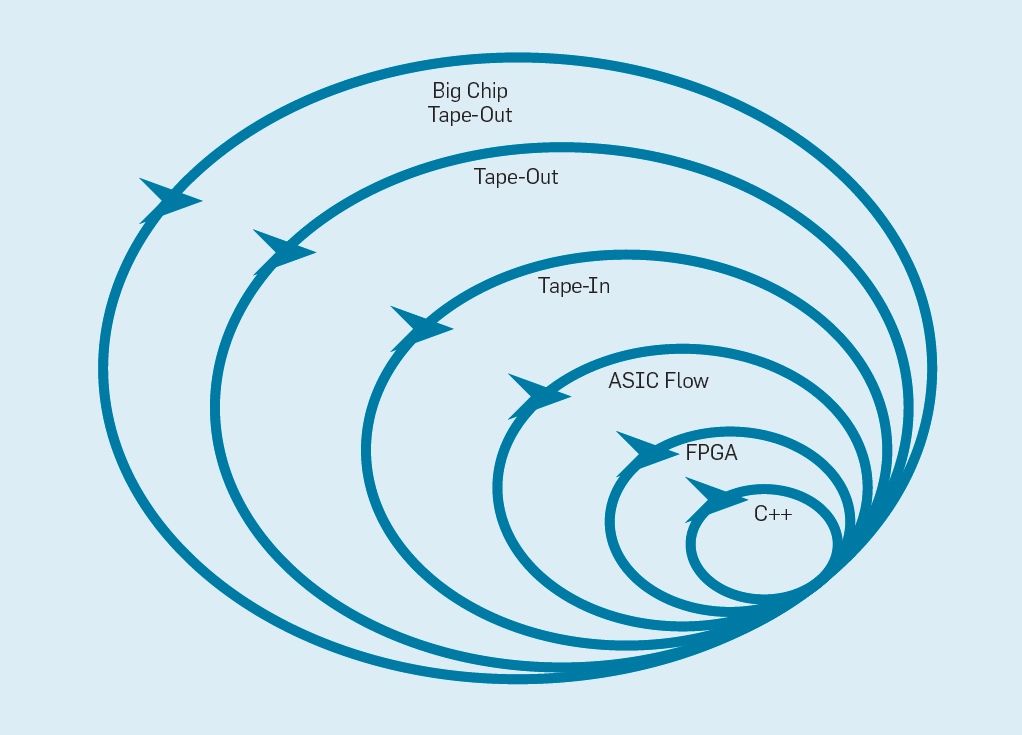

考慮到從設(shè)計(jì)交付到返回芯片所需的幾個(gè)月時(shí)間,稱硬件只需四周的沖刺時(shí)間似乎有些不太可信。圖 9 概述了敏捷開(kāi)發(fā)方法是如何通過(guò)在適當(dāng)?shù)膶由细淖冊(cè)推鹱饔玫摹?strong style="outline: 0px;">最內(nèi)層是軟件模擬器,如果模擬器能夠滿足迭代需求,這是進(jìn)行更改的最方便快捷的地方。第二層是 FPGA,其運(yùn)行速度是具體軟件模擬器的數(shù)百倍。FPGA 可以運(yùn)行操作系統(tǒng)和完整的基準(zhǔn)測(cè)試(像那些來(lái)自標(biāo)準(zhǔn)性能評(píng)估公司的測(cè)試),允許對(duì)原型進(jìn)行更精確的評(píng)估。亞馬遜在云端提供了 FPGA,所以架構(gòu)師們可以使用 FPGA,而無(wú)需購(gòu)買(mǎi)硬件和建立實(shí)驗(yàn)室。為了記錄芯片面積和功率的數(shù)字,第三層使用 ECAD 工具生成芯片布局。即使在工具運(yùn)行之后,在準(zhǔn)備制造新的處理器之前,也需要進(jìn)行一些手動(dòng)步驟來(lái)完善結(jié)果。處理器設(shè)計(jì)者將第四層稱為「tape in」。前四個(gè)層都支持四周沖刺。

出于研究目的,我們可以在 tape in 上停下來(lái),因?yàn)槊娣e、能量和性能估計(jì)非常準(zhǔn)確。但這就像是在長(zhǎng)跑比賽中在離終點(diǎn)約 100 米的地方停下來(lái)一樣,因?yàn)榕懿秸呖梢詼?zhǔn)確預(yù)測(cè)最后時(shí)間。雖然在準(zhǔn)備比賽方面下足了功夫,跑步者仍會(huì)錯(cuò)過(guò)穿過(guò)終點(diǎn)線的興奮和滿足感。硬件工程師相較于軟件工程師的一個(gè)優(yōu)勢(shì)是,他們搭建的是實(shí)物。測(cè)量芯片,運(yùn)行真正的程序,然后向朋友家人展示,這是硬件設(shè)計(jì)的一大樂(lè)趣。

很多研究者覺(jué)得必須停下來(lái),因?yàn)橹圃煨酒某杀咎^(guò)高昂。當(dāng)設(shè)計(jì)作品很小時(shí),它們出奇地便宜。架構(gòu)師只要花 14,000 美元就可以訂購(gòu) 100 個(gè)大小為 1 平方毫米的芯片。在 28 納米制程上,1 平方毫米的芯片可以容納數(shù)百萬(wàn)晶體管,這對(duì) RISC-V 處理器和 NVLDA 處理器來(lái)說(shuō)足夠大了。如果設(shè)計(jì)者的目標(biāo)是設(shè)計(jì)一個(gè)較大的芯片,那最外層的成本將非常高,體系架構(gòu)設(shè)計(jì)者可以用很多小芯片來(lái)闡述很多新想法。

「最黑暗的時(shí)刻,是黎明來(lái)臨之前。」——Thomas Fuller, 1650

要從歷史教訓(xùn)中獲益,架構(gòu)設(shè)計(jì)者們必須意識(shí)到軟件創(chuàng)新也能激勵(lì)架構(gòu)發(fā)展,而提高硬件/軟件界面的抽象水平會(huì)帶來(lái)創(chuàng)新的機(jī)會(huì),市場(chǎng)最終會(huì)解決計(jì)算機(jī)架構(gòu)的爭(zhēng)論。iAPX-432 和 Itanium 說(shuō)明了架構(gòu)投入如何超過(guò)回報(bào),而 S/360、8086 和 ARM 則連續(xù)數(shù)十年帶來(lái)很高的回報(bào),而且將繼續(xù)下去。

登納德縮放定律和摩爾定律的終結(jié),以及標(biāo)準(zhǔn)微處理器性能提升的減速并非必須解決的問(wèn)題,而是公認(rèn)的事實(shí)。這一事實(shí)也提供了驚人的機(jī)會(huì)。高級(jí)、特定領(lǐng)域的語(yǔ)言和架構(gòu)將架構(gòu)師從專有指令集的鏈條中釋放出來(lái),公眾也提高了對(duì)安全性的需求,所有這些將為計(jì)算機(jī)架構(gòu)師帶來(lái)一個(gè)新的黃金時(shí)代。借助開(kāi)源生態(tài)系統(tǒng),敏捷開(kāi)發(fā)的芯片將展示其進(jìn)步,從而加速商業(yè)應(yīng)用。這些芯片中通用處理器的 ISA 理念很可能是 RISC,后者經(jīng)受住了時(shí)間的考驗(yàn)。我們期待著這次能與上一個(gè)黃金時(shí)代一樣快速改善,不過(guò)這次是在成本、能源、安全以及性能方面的改善。

未來(lái)十年,將會(huì)有一場(chǎng)新計(jì)算機(jī)架構(gòu)的寒武紀(jì)爆炸,這對(duì)業(yè)界和學(xué)界的架構(gòu)師們來(lái)說(shuō)將是激動(dòng)人心的時(shí)刻。

參考原文:

https://cacm.acm.org/magazines/2019/2/234352-a-new-golden-age-for-computer-architecture/fulltext

推薦閱讀:

世界的真實(shí)格局分析,地球人類社會(huì)底層運(yùn)行原理

不是你需要中臺(tái),而是一名合格的架構(gòu)師(附各大廠中臺(tái)建設(shè)PPT)

企業(yè)IT技術(shù)架構(gòu)規(guī)劃方案

論數(shù)字化轉(zhuǎn)型——轉(zhuǎn)什么,如何轉(zhuǎn)?

企業(yè)10大管理流程圖,數(shù)字化轉(zhuǎn)型從業(yè)者必備!

【中臺(tái)實(shí)踐】華為大數(shù)據(jù)中臺(tái)架構(gòu)分享.pdf

華為如何實(shí)施數(shù)字化轉(zhuǎn)型(附PPT)

超詳細(xì)280頁(yè)Docker實(shí)戰(zhàn)文檔!開(kāi)放下載