多核之后,CPU 的發(fā)展方向是什么?

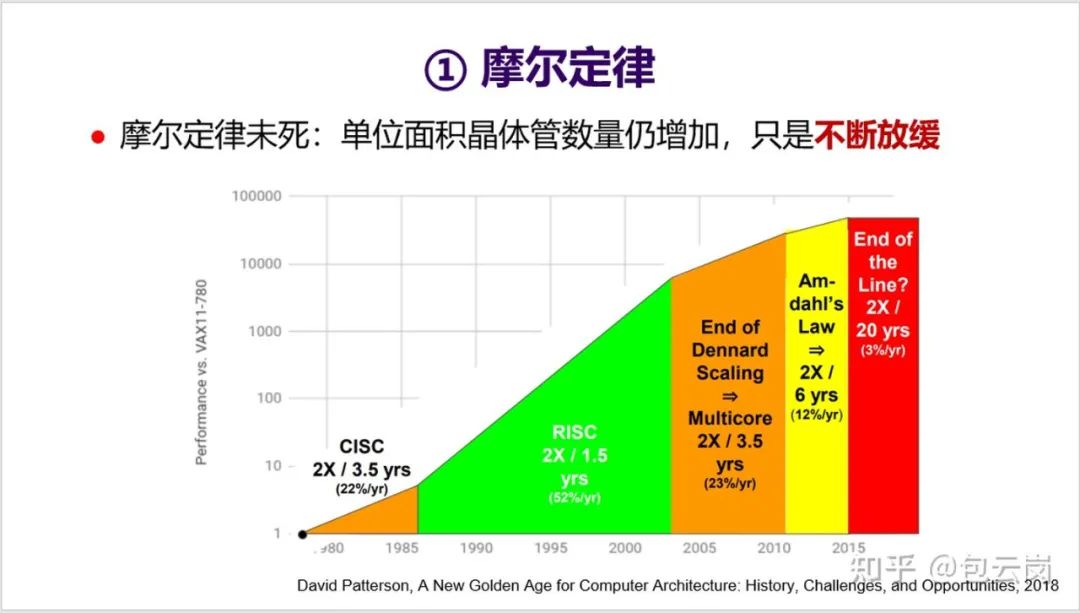

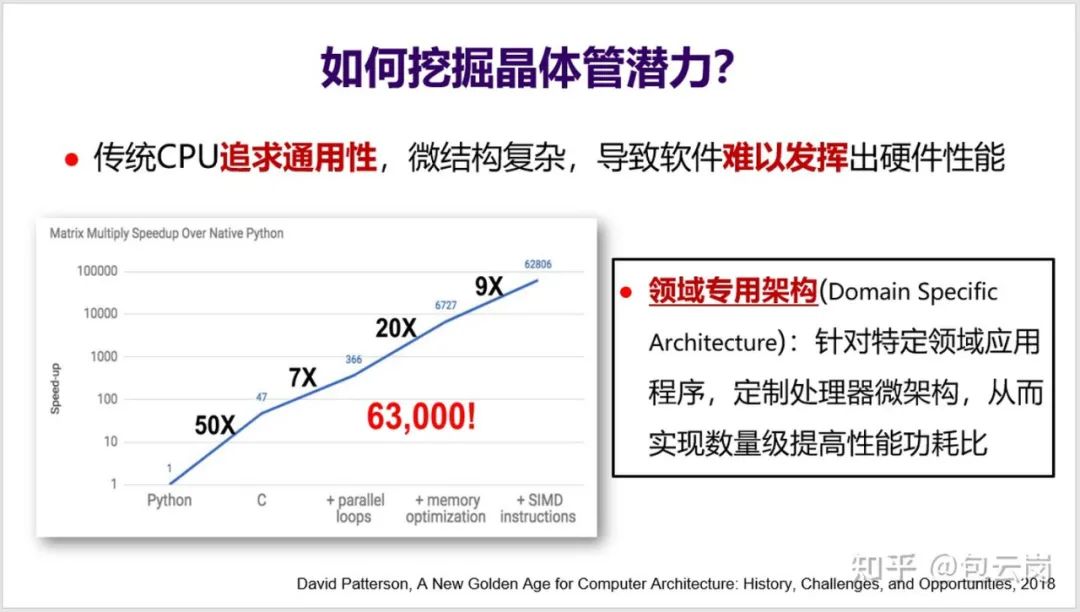

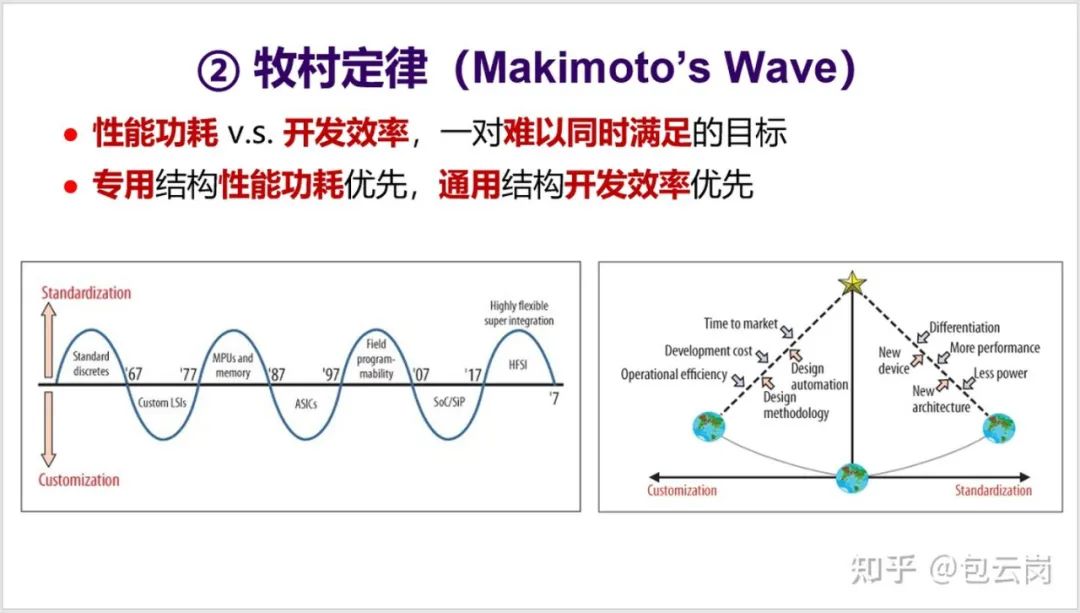

后摩爾定律時(shí)代,CPU 性能提升放緩,計(jì)算力增長(zhǎng)式微。多核之后,CPU 還能借助哪些方向?qū)崿F(xiàn)突圍?在這篇文章中,中國(guó)科學(xué)院計(jì)算技術(shù)研究所研究員包云崗對(duì)這一問(wèn)題進(jìn)行了詳細(xì)解讀。

作者簡(jiǎn)介

包云崗,中國(guó)科學(xué)院計(jì)算技術(shù)研究所研究員、博士生導(dǎo)師、中國(guó)科學(xué)院大學(xué)教授,中國(guó)開(kāi)放指令生態(tài)(RISC-V)聯(lián)盟秘書(shū)長(zhǎng),從事計(jì)算機(jī)體系結(jié)構(gòu)和開(kāi)源芯片方向前沿研究,主持研制多款達(dá)到國(guó)際先進(jìn)水平的原型系統(tǒng),相關(guān)技術(shù)在華為、阿里等國(guó)內(nèi)外企業(yè)應(yīng)用。他曾獲「CCF-Intel 青年學(xué)者」獎(jiǎng)、阿里巴巴最佳合作項(xiàng)目獎(jiǎng)、「CCF-IEEE CS」青年科學(xué)家獎(jiǎng)等獎(jiǎng)項(xiàng)。

評(píng)論

圖片

表情