AMD Zen 4架構(gòu)路標:2022年Genoa 96核,2023年Bergamo 128核

導(dǎo)讀:今年7月,英特爾公布了新的路線圖,4年內(nèi)要完成5代產(chǎn)品迭代,推出IDM2.0戰(zhàn)略快速進入Intel 20A制程工藝,參見“英特爾技術(shù)創(chuàng)新戰(zhàn)略線路圖”。AMD和Intel在芯片領(lǐng)域的尖峰對決一直沒有停歇。

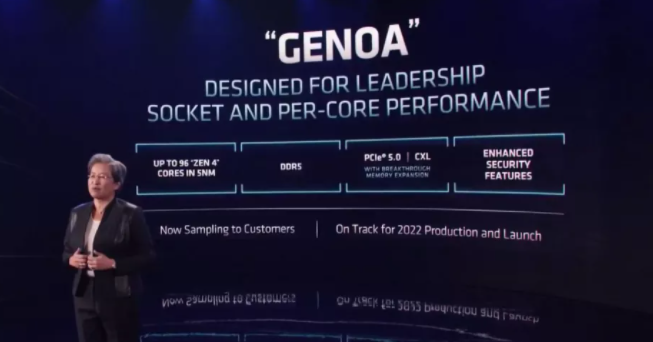

AMD 首席執(zhí)行官 Lisa Su 今天在其 AMD 加速數(shù)據(jù)中心活動中分享了該公司的 Zen 4 CPU 路線圖,包括 96 核 Genoa 型號和 128 核 Bergamo 芯片。在 AMD 推出具有高達 768MB 三級緩存和 Instinct MI250X GPU的EPYC Milan-X 芯片之后,這為活動增添了不少亮點。

AMD 還分享了其將用于新 Genoa 和 Bergamo 芯片的 5nm TSMC 工藝的第一個細節(jié),聲稱與 AMD 用于其當前一代芯片的 7nm 工藝相比,它提供兩倍的密度和功率效率以及 1.25 倍的性能。

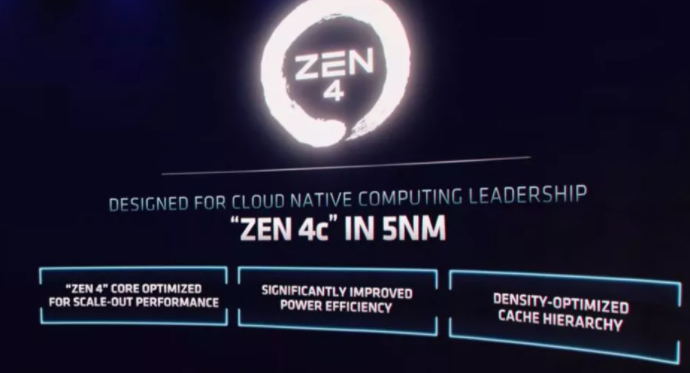

新路線圖涵蓋第四代 EYPC 處理器。其中96 核 Genoa 將在 2022 年亮相,采用 5nm 工藝,而同樣采用 5nm 工藝的 128 核 Bergamo 將于 2023 年上市。此外,Bergamo 還配備了一種新型的“Zen 4c”內(nèi)核,針對特定用例,這意味著 AMD 的 Zen 4 芯片將配備兩種類型的內(nèi)核,大概鬧鐘功能的“c”內(nèi)核顯然是較小的變體。

這是 AMD 針對 Zen 4 CPU 路線圖的 TLDR:

“Genoa”將擁有多達96個高性能“Zen 4”內(nèi)核,在DDR5和PCIe Gen 5中實現(xiàn)下一代內(nèi)存和I/O技術(shù),并驅(qū)動平臺能力完美平衡Zen 4內(nèi)核、內(nèi)存和I /O 提供領(lǐng)先的效率;

“Bergamo”是一種高核數(shù)計算引擎,專為需要高密度線程密度的云原生應(yīng)用程序而定制。擁有 128 個高性能“Zen 4 C”內(nèi)核;

“Bergamo”具有與 Genoa相同的所有功能,包括DDR5、PCIe 5、CXL 1.1、相同的RAS和全套Infinity Guard安全功能,并且與熱那亞插座兼容

Genoa將采用臺積電的 5nm 工藝,AMD 表示,5nm 的密度和功率效率是為當前一代 EPYC Milan 芯片提供動力的 7nm 工藝的兩倍。它還提供 7nm 工藝 1.25 倍的性能。這對于以消費者為中心的 Ryzen Zen 4 芯片來說也是個好兆頭。

EPYC Genoa 芯片將擁有多達 96 個 Zen 4 內(nèi)核并支持 DDR5 和 PCIe 5.0,以及允許設(shè)備之間一致內(nèi)存連接的CXL 1.1 接口。該芯片將解決 HPC 和通用數(shù)據(jù)中心、企業(yè)和云工作負載,Su 表示它將擴展每核和socket級(多線程)性能。Genoa現(xiàn)在正在向客戶提供樣品,并有望在 2022 年推出。

Bergamo 也采用 5nm 工藝制造,單個芯片中將配備多達 128 個內(nèi)核。

AMD 創(chuàng)造了一種新的“Zen 4c”類型的 Zen 4 核心,“c”表示該核心專為云原生工作負載而設(shè)計。Zen 4c 內(nèi)核在 5nm EPYC Bergamo 中首次亮相,它與 Genoa 插槽兼容,并使用相同的 Zen 4 指令集。這意味著您可以將這些芯片放入與 Genoa 型號相同的服務(wù)器中。

這些“c”核心可能比將在Genoa 首次亮相的標準 Zen 4 核心小,在其中刪除了某些不需要的功能以提高計算密度。但是,這些芯片具有密度優(yōu)化的緩存層次結(jié)構(gòu)以增加內(nèi)核數(shù)量,從而解決需要更高線程密度的云工作負載。這可能意味著芯片具有較小的緩存,或者緩存級別可能已被刪除,但 AMD 尚未分享詳細信息。

AMD 確實表示,Bergamo 將提供更高水平的電源效率和每個插槽的性能。Bergamo 將于 2023 年上半年發(fā)貨。它具有與熱那亞相同的整體功能集,因此具有 PCIe 5.0、DDR5 和 CXL 1.1。

隨著 AMD 越來越接近推出這些處理器,我們一定會了解更多。敬請關(guān)注。

AMD Zen 4架構(gòu)細節(jié)曝光

日前,業(yè)內(nèi)人士Hans de Vries曝光了Zen 4的部分CPU設(shè)計架構(gòu)細節(jié),據(jù)說來自前不久某硬件大廠遭勒索軟件攻擊后泄露到黑市的機密文檔。

圖標概述了Zen 4的緩存部分,對比Zen3,一級指令/數(shù)據(jù)緩存大小沒變,依然是32KB、關(guān)聯(lián)8路,但二級緩存(指令+數(shù)據(jù))則從512KB翻番到1MB,依舊是關(guān)聯(lián)8路。

遺憾的是,三級緩存的容量未公布,看來有驚喜,上一代Zen3是每個CCD(8核Die)共享32MB。

不過可以比較12代酷睿Alder Lake體系中,Golden Cove(P核,性能核)每個核心1.25MB二級緩存,Gracemont(能效核,E核)則是每四個核心2MB,也就是二級緩存最多14MB,這意味著Zen4的物理16核(16MB L2)會再次反超。

通常來說一級、二級緩存在分支預(yù)測中扮演極為重要的角色,它也是IPC指標增幅的重要支撐。按照AMD此前的說法,Zen4之于Zen3的變化幅度不會小于Zen3之于Zen2,后者的IPC當時增加了19%,5nm Zen4非常可期,況且還有后發(fā)優(yōu)勢一說。

深度報告:RISC-V異構(gòu)IoT全新架構(gòu)

2、信創(chuàng)產(chǎn)業(yè)研究框架

3、ARM行業(yè)研究框架

4、CPU研究框架

5、國產(chǎn)CPU研究框架

6、行業(yè)深度報告:GPU研究框架

2021年信創(chuàng)產(chǎn)業(yè)發(fā)展報告

信創(chuàng)產(chǎn)業(yè)系列專題(總篇)

中國信創(chuàng)產(chǎn)業(yè)發(fā)展白皮書(2021)

來源:智能計算芯架構(gòu)

轉(zhuǎn)載申明:轉(zhuǎn)載本號文章請注明作者和來源,本號發(fā)布文章若存在版權(quán)等問題,請留言聯(lián)系處理,謝謝。

推薦閱讀

更多架構(gòu)相關(guān)技術(shù)知識總結(jié)請參考“架構(gòu)師全店鋪技術(shù)資料打包”相關(guān)電子書(37本技術(shù)資料打包匯總詳情可通過“閱讀原文”獲取)。

全店內(nèi)容持續(xù)更新,現(xiàn)下單“全店鋪技術(shù)資料打包(全)”,后續(xù)可享全店內(nèi)容更新“免費”贈閱,價格僅收198元(原總價350元)。

溫馨提示:

掃描二維碼關(guān)注公眾號,點擊閱讀原文鏈接獲取“架構(gòu)師技術(shù)全店資料打包匯總(全)”電子書資料詳情。