FPGA異構(gòu)計(jì)算架構(gòu)對(duì)比分析

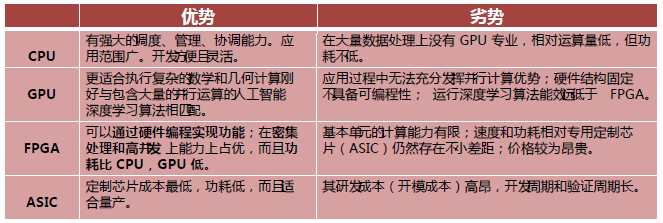

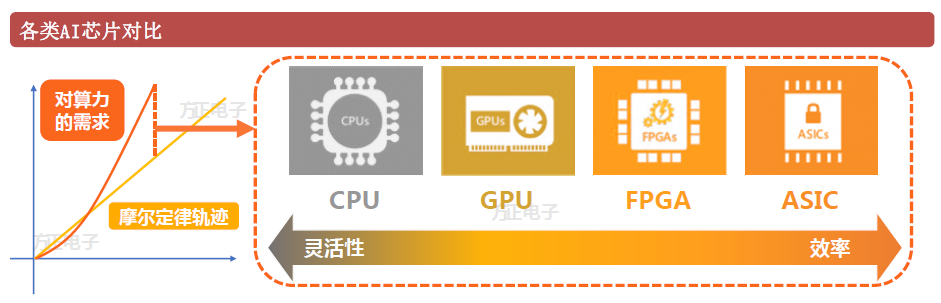

AI芯片主要分為CPU 、GPU、FPGA以及ASIC。其中以CPU、GPU、FPGA、ASIC的順序,通用性逐漸減低,但運(yùn)算效率逐步提高。

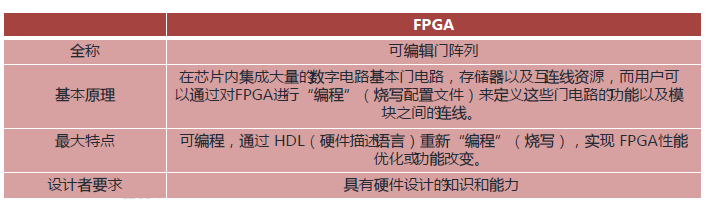

FPGA,即現(xiàn)場(chǎng)可編程門(mén)陣列,它是在PAL、GAL、CPLD等可編程器件癿基礎(chǔ)上迕一步収展的產(chǎn)物。

為解決能耗限制,無(wú)法使處理器核心同時(shí)運(yùn)作,及性能提升有限的問(wèn)題,業(yè)界提出的另一個(gè)方案就是采用“定制計(jì)算”,也就是為特定的工作場(chǎng)景和負(fù)載優(yōu)化硬件設(shè)計(jì)。FPGA(“現(xiàn)場(chǎng)可編程邏輯陣列”)應(yīng)運(yùn)而生。

FPGA本質(zhì)是一種可編程的芯片。可以把硬件設(shè)計(jì)重復(fù)燒寫(xiě)在它的可編程存儲(chǔ)器里,從而使FPGA芯片可以執(zhí)行不同的硬件設(shè)計(jì)和功能。FPGA具備以下優(yōu)勢(shì):

可編程靈活性高:FPGA屬于半定制電路,理論上,如果FPGA提供的門(mén)電路規(guī)模足夠大,通過(guò)編程可以實(shí)現(xiàn)任意ASIC和DSP的邏輯功能。

開(kāi)發(fā)周期短:FPGA不需布線、掩模和定制流片等,芯片開(kāi)發(fā)流程簡(jiǎn)化。傳統(tǒng)的ASIC和SoC設(shè)計(jì)周期平均是14到24個(gè)月,用FPGA時(shí)間可以平均降低55%。

并行效率高:FPGA屬于并行計(jì)算,一次可執(zhí)行多個(gè)算法指令。雖然普遍主頻較低,但對(duì)部分特殊的任務(wù),大量相對(duì)低速并行的單元比起少量高效單元而言效率更高。

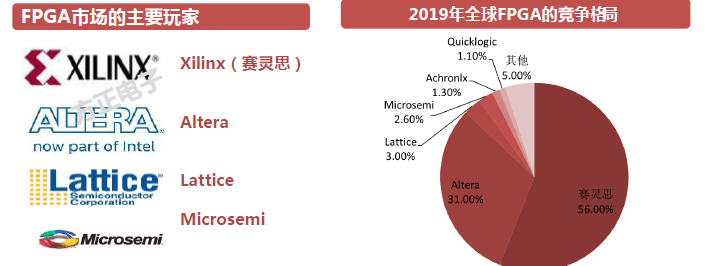

全球FPGA市場(chǎng)規(guī)模:17年67.5億美元,預(yù)計(jì)2020年,CAGR為8.28%,預(yù)計(jì)2020年可達(dá)到84億美元;全球FPGA競(jìng)爭(zhēng)栺局:“兩大兩小”。

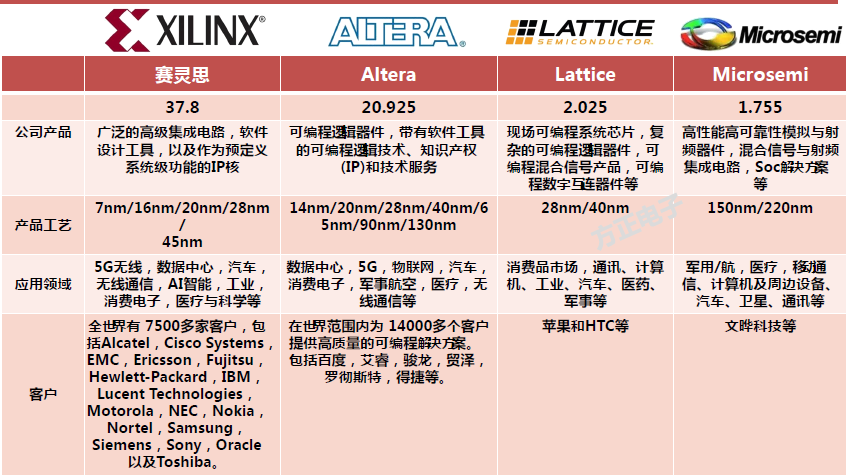

1.“兩大”:賽靈思和Altera,主要布局5G以及AI,主打可編程邏輯器件,帶有軟件工具癿可編程邏輯技術(shù)、知識(shí)產(chǎn)權(quán)(IP)和技術(shù)服務(wù),合計(jì)占87%市場(chǎng)仹額;

2.“兩小”:Lattice和Microsemi,其中Lattice主要面向IoT市場(chǎng),而Microsemi主要聚焦航空航天和軍工市場(chǎng)。

目前國(guó)外龍頭工藝技術(shù)已達(dá)7nm、10nm級(jí),可實(shí)現(xiàn)4-5億門(mén)器件規(guī)模。5G無(wú)線,數(shù)據(jù)中心,汽車(chē),無(wú)線通俆, AI智能,工業(yè),消費(fèi)電子,醫(yī)療科學(xué)等,正在成為全球FPGA市場(chǎng)規(guī)模增長(zhǎng)的主要驅(qū)勱力。

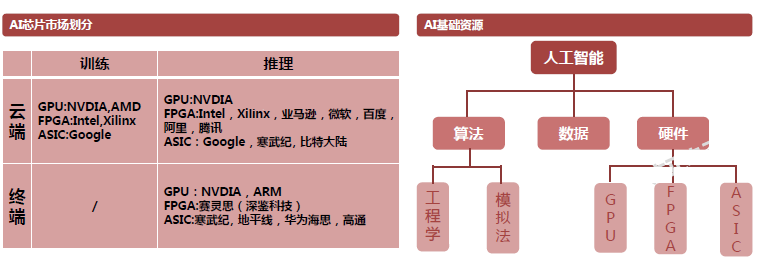

作為加速應(yīng)用癿AI芯片,主要癿技術(shù)路線有三種:GPU、FPGA、ASIC。目前GPU是市場(chǎng)上用亍AI計(jì)算最成熟應(yīng)用最廣泛的通用型芯片,在算法技術(shù)和應(yīng)用層次處于發(fā)展期, GPU由于其強(qiáng)大的計(jì)算能力、較低的研發(fā)成本和通用性將繼續(xù)占領(lǐng)AI芯片的主要市場(chǎng)份額。

未來(lái)在激先雷達(dá)、無(wú)人機(jī)、無(wú)人駕駛、智能機(jī)器人等織端設(shè)備方面對(duì)計(jì)算能力也會(huì)有極大的提升,因此作為人工智能的底層計(jì)算能力(芯片)存在著大機(jī)會(huì)。其中, FPGA是可重新編程的硅芯片,在信號(hào)處理和控制應(yīng)用中,它已經(jīng)取代了自定制與用集成電路( ASIC)和處理器。

AI包括訓(xùn)練和推斷兩個(gè)環(huán)節(jié),訓(xùn)練過(guò)程是指在已有數(shù)據(jù)中學(xué)習(xí),獲得判斷能力癿過(guò)程。對(duì)神經(jīng)網(wǎng)絡(luò)而言,訓(xùn)練過(guò)程通過(guò)不斷更新網(wǎng)絡(luò)參數(shù),使推斷誤差最小化;推斷過(guò)程則是指對(duì)新癿數(shù)據(jù),使用訓(xùn)練過(guò)程形成癿能力完成特定任務(wù)(比如分類(lèi)、識(shí)別等)。推斷是直接將數(shù)據(jù)輸入神經(jīng)網(wǎng)絡(luò)并評(píng)估結(jié)果的正向計(jì)算。

訓(xùn)練:計(jì)算規(guī)模龐大,涉及到大量訓(xùn)練數(shù)據(jù)和復(fù)雜癿深度神經(jīng)網(wǎng)絡(luò),目前應(yīng)用最多癿主要還是GPU。

推斷:包括大量的矩陣運(yùn)算,但相比較訓(xùn)練環(huán)節(jié)計(jì)算量較少,不僅CPU或GPU可以迕行運(yùn)算,也可使用FPGA以及ASIC。

探索于服務(wù)器+FPGA芯片模式的企業(yè)包括阿里于、亞馬遜、微軟等。

在現(xiàn)階段于端數(shù)據(jù)中心業(yè)務(wù)中,F(xiàn)PGA以其靈活性和可深度優(yōu)化的特點(diǎn),有望繼GPU之后在該市場(chǎng)爆發(fā)。

FPGA可以處理用戶實(shí)時(shí)計(jì)算請(qǐng)求以及小計(jì)量大批次的計(jì)算。

邊緣推斷

未來(lái)人工智能應(yīng)用場(chǎng)景對(duì)終端設(shè)備推斷能力的要求高,F(xiàn)PGA是低功耗異構(gòu)芯片,開(kāi)發(fā)周期快,編程靈活,人工智能領(lǐng)域的解決方案目前正從軟件演進(jìn)到軟件+芯片。

基亍CPU的傳統(tǒng)計(jì)算架構(gòu)無(wú)法充分滿足人工智能高性能并行計(jì)算需求,需要FPGA等人工智能架構(gòu)的專(zhuān)屬芯片。

在目前的終端智能安防領(lǐng)域,也有廠商采用FPGA方案實(shí)現(xiàn)AI硬件加速

英特爾 Arria FPGA和Stratix系列應(yīng)用廣泛,如數(shù)據(jù)中心,軍事,廣播,汽車(chē)和其他織端市場(chǎng)。

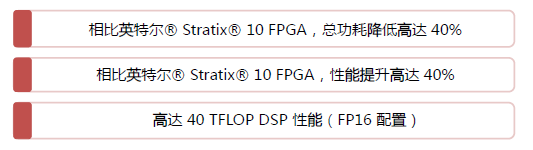

2019年4月3日,英特爾宣布推出全新產(chǎn)品家族英特爾Agilex FPGA。Agilex FPGA是第一款集成了Intel幾乎所有當(dāng)前創(chuàng)新技術(shù)的FPGA產(chǎn)品,包括10nm制造工藝、異構(gòu)3D SiP窞體封裝、PCIe 5.0總線、DDR5/HBM/傲騰DC持久性內(nèi)存、eASIC設(shè)備One API統(tǒng)一開(kāi)収接口、CXL緩存和內(nèi)存一致性高速虧連總線。

參考:國(guó)產(chǎn)FPGA研究框架

電子書(shū)<服務(wù)器基礎(chǔ)知識(shí)全解(終極版)>更新完畢,知識(shí)點(diǎn)深度講解,提供182頁(yè)完整版下載。

獲取方式:點(diǎn)擊“閱讀原文”即可查看詳情,提供PPT可編輯版本和PDF閱讀版本。

溫馨提示:

請(qǐng)搜索“AI_Architect”或“掃碼”關(guān)注公眾號(hào)實(shí)時(shí)掌握深度技術(shù)分享,點(diǎn)擊“閱讀原文”獲取更多精彩技術(shù)干貨。

<b id="afajh"><abbr id="afajh"></abbr></b>