發(fā)力3.5D先進封裝技術?三星組建半導體封裝工作組

雖然在半導體先進制程工藝方面,近日三星成功搶先臺積電量產(chǎn)了3nm GAA制程工藝,但是在2.5/3D先進封裝技術方面,三星仍落后于英特爾和臺積電。而為了縮小這方面的差距,三星也已經(jīng)組建了新的半導體封裝工作組發(fā)力先進封裝技術。

據(jù)韓國媒體BusinessKorea報導,三星DS 部門已于6月中旬組建了半導體封裝工作組,由直屬DS 部門CEO Kyung Kye-hyun直接管轄。該半導體封裝工作組由DS 部門測試與系統(tǒng)封裝(TSP) 工程師、半導體研發(fā)中心研究人員及存儲和代工部門相關人員組成,預計將推出新的先進封裝解決方案,加強與有著封裝業(yè)務需求的大型代工客戶合作。

報道稱,三星此舉代表其對于先進封裝技術的重視程度。特別是在目前先進制程工藝微縮越來越困難,成本也越來越高的背景之下,通過先進封裝技術將多個芯片進行異質(zhì)整合,或?qū)鹘y(tǒng)大芯片拆分成多個小芯片通過先進封裝技術進行整合的Chiplet方案,成為了新的方向。而這其中,先進封裝技術則是關鍵。

根據(jù)市場研究公司Yole Development的報告顯示,英特爾和臺積電分占2022 年全球先進封裝投資32% 和27%,三星僅排名第四,甚至落后臺灣封裝測試大廠日月光投控。

早在2017年英特爾就推出了EMIB(Embedded Multi-Die Interconnect Bridge,嵌入式多核心互聯(lián)橋接)封裝技術相結(jié)合,可以將不同類型、不同制程的小芯片IP以2.5D的形式靈活組合在一起,形成一個類似SoC的結(jié)構。

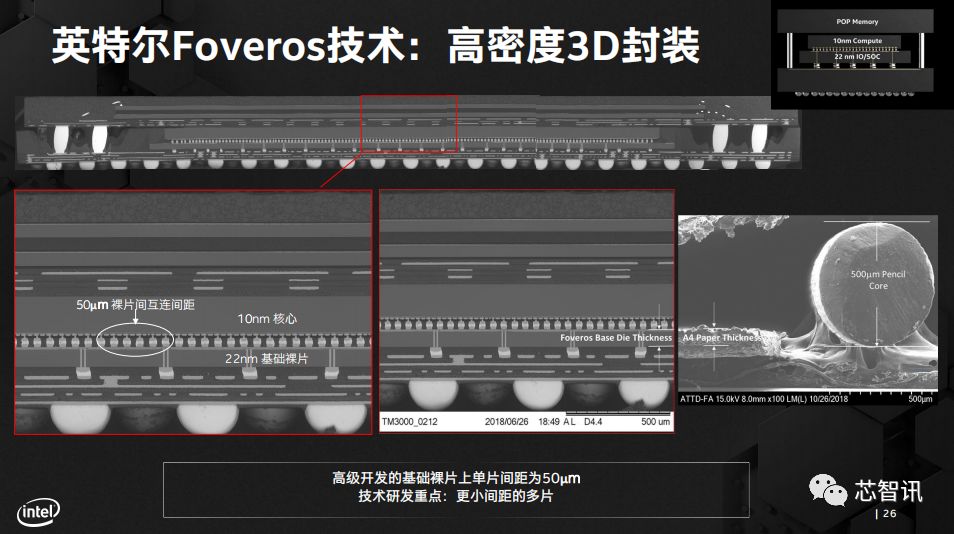

2018年底,英特爾又推出了業(yè)界首創(chuàng)的3D邏輯芯片封裝技術——Foveros 3D,它可實現(xiàn)在邏輯芯片上堆疊不同制程的邏輯芯片。以前只能把邏輯芯片和存儲芯片連在一起,因為中間的帶寬和數(shù)據(jù)要求要低一些。而Foveros 3D則可以把不同制程的邏輯芯片堆疊在一起,裸片間的互聯(lián)間隙只有50μm,同時可保證連接的帶寬足夠大、速度夠快、功耗夠低,而且3D的堆疊封裝形式,還可以保持較小的面積。2020年,英特爾推出了基于Foveros 技術生產(chǎn)的代號為“Lakefield”的處理器。2021年7月,英特爾還宣布計劃推出Foveros Direct技術,可以實現(xiàn)10微米以下的凸點間距,使3D堆疊的互連密度提高一個數(shù)量級。

除了英特爾之外,臺積電在先進封裝領域也布局多年。目前,臺積電已將2.5D和3D先進封裝相關技術整合為“3DFabric”平臺,可讓客戶們自由選配,前段技術包含3D的整合芯片系統(tǒng)(SoIC InFO-3D),后段組裝測試相關技術包含2D/2.5D的整合型扇出(InFO)以及2.5D的CoWoS系列家族。值得一提的是,臺積電還在日本筑波建了3D IC研發(fā)中心,該研發(fā)中心已于今年6月24日開始啟用。

雖然三星較早也推出了2.5D封裝技術I-Cube,可將一個或多個邏輯晶片(如CPU、GPU 等) 和多個存儲芯片(如高頻寬存儲器、HBM) 整合連結(jié)放置在硅中介層( Interposer) 的頂部,進一步使多個芯片為整合為單個元件工作。2020年8月,三星又宣布推出了新一代3D封裝技術——X-Cube,基于TSV硅穿孔技術將不同芯片堆疊,比如可以將SRAM堆疊到芯片上方,釋放了占用空間,可以堆疊更多內(nèi)存芯片,目前已經(jīng)可以用于7nm及5nm工藝。但是,不論是從技術領先性和商用情況來看,三星在先進封裝技術方式仍落后于英特爾和臺積電。

值得注意的是,三星除了2020 年推出3D封裝技術“X-Cube”之外,三星DS 部門還曾在2021年6 月的Hot Chips大會上表示,正在開發(fā)3.5D先進封裝技術,但是三星并未透露具體的細節(jié)。

此次三星先進封裝工作組的成立,顯然意味著三星將進一步加大對于先進封裝技術的投入,但是能否成功找到方法,縮小與英特爾、臺積電在先進封裝領域的差距,將是市場關注的重點。

編輯:芯智訊-浪客劍

相關文章:

《后摩爾時代的“助推劑”:Chiplet到底有何優(yōu)勢,挑戰(zhàn)又有哪些?》

四萬字詳解ASML的崛起之路:“三大戰(zhàn)役”如何成就“最強王者”?

星紀時代戰(zhàn)略投資魅族科技,拿下79.09%控股權!黃章任產(chǎn)品戰(zhàn)略顧問

集創(chuàng)北方科創(chuàng)板IPO:拿下多個市場第一,與華為、vivo存在對賭協(xié)議

蘋果砍單10%,AMD砍單2萬片晶圓,美光減產(chǎn)!通用MCU也現(xiàn)砍單降價潮!

三星宣布3nm量產(chǎn)!真領先臺積電,還是“趕鴨子上架”?GAA技術有何優(yōu)勢?

Arm發(fā)布全新CPU/GPU IP:Cortex-X3性能提升34%,新旗艦GPU可支持光線追蹤

臺灣76家半導體上市公司平均薪資曝光:最高人均138.2萬元/年!聯(lián)發(fā)科第3

中芯國際:結(jié)構性短缺將持續(xù),堅定支持設備材料國產(chǎn)化!

行業(yè)交流、合作請加微信:icsmart01

芯智訊官方交流群:221807116