ASIC芯片基礎(chǔ)知識(shí)全解(附下載)

ASIC (Application Specific Integrated Circuit )芯片是專(zhuān)用集成電路,是針對(duì)用戶(hù)對(duì)特定電子系統(tǒng)的需求,從根級(jí)設(shè)計(jì)、制造的專(zhuān)有應(yīng)用程序芯片,其計(jì)算能力和計(jì)算效率可根據(jù)算法需要進(jìn)行定制,是固定算法最優(yōu)化設(shè)計(jì)的產(chǎn)物。ASIC 芯片模塊可廣泛應(yīng)用于人工智能設(shè)備、虛擬貨幣挖礦設(shè)備、耗材打印設(shè)備、軍事國(guó)防設(shè)備等智慧終端。

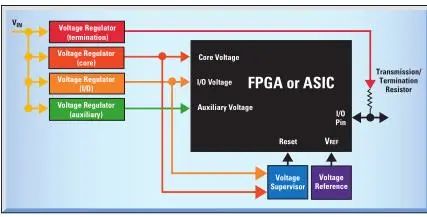

在硬件層面,ASIC 芯片由基本硅材料、磷化鎵、砷化鎵、氮化鎵等材料構(gòu)成。在物理結(jié)構(gòu)層面,ASIC 芯片模塊由外掛存儲(chǔ)單元、電源管理器、音頻畫(huà)面處理器、網(wǎng)絡(luò)電路等IP核拼湊而成。同一芯片模組可搭載一個(gè)或幾個(gè)功能相同或不同的ASIC 芯片,以滿(mǎn)足一種或多種特定需求。

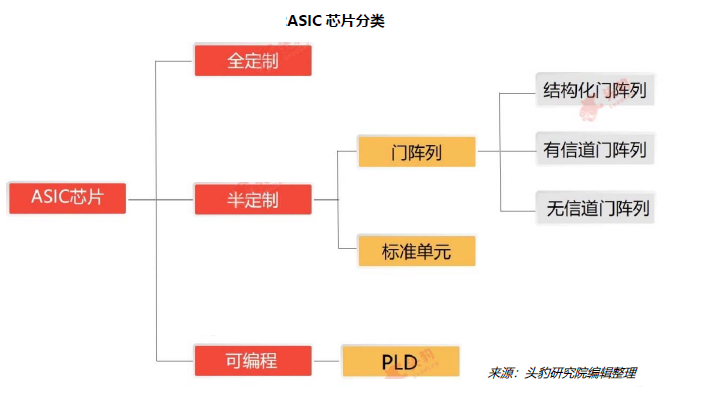

(1) 根據(jù)定制程度不同,ASIC 芯片可被分為全定制ASIC 芯片、半定制ASIC 芯片及可編程ASIC芯片。

全定制ASIC 芯片是定制程度最高的芯片之一,研發(fā)人員基于不同電路結(jié)構(gòu)設(shè)計(jì)針對(duì)不同功能的邏輯單元,于芯片板搭建模擬電路、存儲(chǔ)單元、機(jī)械結(jié)構(gòu)。邏輯單元之間由掩模版連接,ASIC 芯片掩模版也具備高度定制化特點(diǎn)。

全定制化ASIC 芯片設(shè)計(jì)成本較高,平均每單位芯片模塊設(shè)計(jì)時(shí)間超過(guò)9 周。該類(lèi)芯片通常用于高級(jí)應(yīng)用程序。

相對(duì)半定制化ASIC 芯片,全定制化ASIC 芯片在性能、功耗等方面表現(xiàn)優(yōu)秀。如應(yīng)對(duì)相同功能,在同種工藝前提下,全定制化ASIC 芯片平均算力輸出約為半定制化ASIC 芯片平均算力輸出的8 倍,采用24 納米制程的全定制化ASIC 芯片在性能上優(yōu)于采用5 納米制程的半定制化ASIC 芯片。

構(gòu)成半定制ASIC 芯片的邏輯單元大部分取自標(biāo)準(zhǔn)邏輯單元庫(kù),部分根據(jù)特定需求做自定義設(shè)計(jì)。相對(duì)全定制ASIC 芯片設(shè)計(jì)成本較低,靈活度較高。

門(mén)陣列ASIC 芯片包括有信道門(mén)陣列、無(wú)信道門(mén)陣列和結(jié)構(gòu)化門(mén)陣列。門(mén)陣列ASIC 芯片結(jié)構(gòu)中硅晶片上預(yù)定晶體管位置不可改變,設(shè)計(jì)人員多通過(guò)改變芯片底端金屬層等方式調(diào)整邏輯單元互連結(jié)構(gòu)。

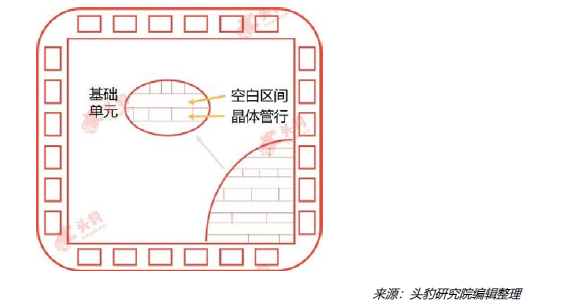

有信道門(mén)陣列ASIC 芯片:該類(lèi)芯片晶體管位置高度固定,設(shè)計(jì)人員可在晶體管行之間預(yù)定義的空白空間進(jìn)行電路布局;

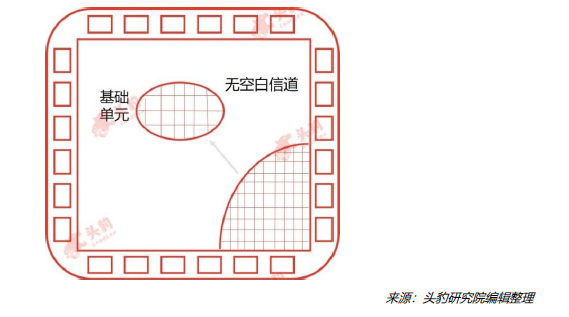

無(wú)信道門(mén)陣列ASIC 芯片:無(wú)信道結(jié)構(gòu)下,晶體管行之間不存在電路布局空間,設(shè)計(jì)人員通常于門(mén)陣列單元上方進(jìn)行布線;

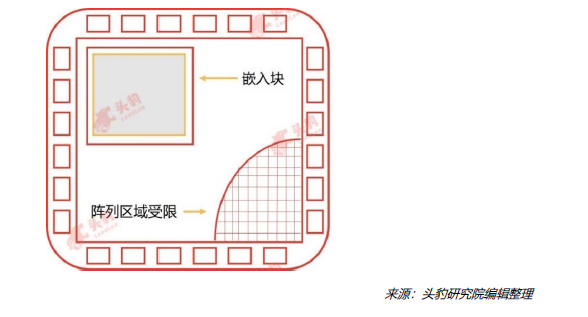

結(jié)構(gòu)化門(mén)陣列ASIC 芯片:該結(jié)構(gòu)包括基本門(mén)陣列行及嵌入塊。嵌入塊可提高線路布局靈活度,但對(duì)芯片體積構(gòu)成限制。該結(jié)構(gòu)下,線路布局面積使用效率較高,設(shè)計(jì)成本較低,周轉(zhuǎn)時(shí)間較短。

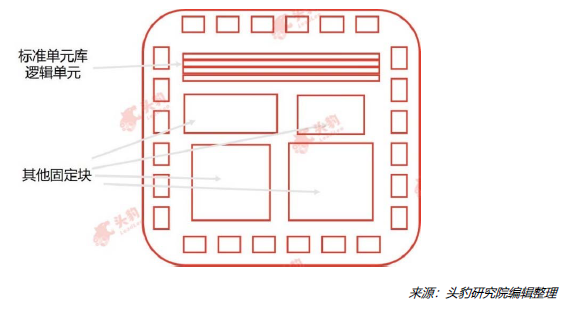

b、 標(biāo)準(zhǔn)單元

該類(lèi)ASIC 芯片由選自標(biāo)準(zhǔn)單元庫(kù)的邏輯單元構(gòu)成。設(shè)計(jì)人員可按算法需求自行布置標(biāo)準(zhǔn)單元。除標(biāo)準(zhǔn)單元外,微控制器、微處理器等固定塊也可用于標(biāo)準(zhǔn)單元ASIC 芯片架構(gòu)。

③ 可編程ASIC 芯片

廣義而言,可編程ASIC 芯片可分為FPGA 芯片和PLD 芯片。在實(shí)際生產(chǎn)過(guò)程中,將FPGA 芯片列為不同于ASIC 芯片的研究機(jī)構(gòu)和企業(yè)數(shù)量不斷增加,故本報(bào)告僅將PLD(Programmable Logic Device)視為可編程ASIC 芯片子類(lèi)別。

PLD 亦稱(chēng)可編程邏輯器件,在結(jié)構(gòu)上包括基礎(chǔ)邏輯單元矩陣、觸發(fā)器、鎖存器等,其互連部分作為單個(gè)模塊存在。設(shè)計(jì)人員通過(guò)對(duì)PLD 進(jìn)行編程以滿(mǎn)足部分定制應(yīng)用程序需求。

① TPU 為張量處理器,專(zhuān)用于機(jī)器學(xué)習(xí)。如Google 于2016 年5 月研發(fā)針對(duì)

Tensorflow 平臺(tái)的可編程AI 加速器,其內(nèi)部指令集在Tensorflow 程序變化或更新算法時(shí)可運(yùn)行。

② BPU 是大腦處理器,是由地平線科技提出的嵌入式人工智能處理器架構(gòu)。

③ NPU 是神經(jīng)網(wǎng)絡(luò)處理器,在電路層模擬人類(lèi)神經(jīng)元和突觸,并用深度學(xué)習(xí)指令集直接處理大規(guī)模電子神經(jīng)元和突觸數(shù)據(jù)。

CPU 等傳統(tǒng)芯片通過(guò)讀取、執(zhí)行外部程序代碼指令而生成結(jié)果,相對(duì)而言,ASIC 芯片讀取原始輸入數(shù)據(jù)信號(hào),并經(jīng)內(nèi)部邏輯電路運(yùn)算后直接生成輸出信號(hào)。

相對(duì)CPU、GPU、FPGA 等類(lèi)型芯片,ASIC 芯片在專(zhuān)用系統(tǒng)應(yīng)用方面具備多元優(yōu)勢(shì),具體表現(xiàn)在如下幾方面。

① 面積優(yōu)勢(shì):ASIC 芯片在設(shè)計(jì)時(shí)避免冗余邏輯單元、處理單元、寄存器、存儲(chǔ)單元等架構(gòu),以純粹數(shù)字邏輯電路形式構(gòu)建,有利于縮小芯片面積。應(yīng)對(duì)小面積芯片,同等規(guī)格晶圓可被切割出更多數(shù)量芯片,有助于企業(yè)降低晶圓成本。

② 能耗優(yōu)勢(shì):ASIC 芯片單位算力能耗相對(duì)CPU、GPU、FPGA 較低,如GPU 每算力平均約消耗0.4 瓦電力,ASIC 單位算力平均消耗約0.2 瓦電力,更能滿(mǎn)足新型智能家電對(duì)能耗的限制。

③ 集成優(yōu)勢(shì):因采用定制化設(shè)計(jì),ASIC 芯片系統(tǒng)、電路、工藝高度一體化,有助于客戶(hù)獲得高性能集成電路。

④ 價(jià)格優(yōu)勢(shì):受到體積小、運(yùn)行速度高、功耗低等特點(diǎn)影響,ASIC 芯片價(jià)格遠(yuǎn)低于CPU、GPU、FPGA 芯片。當(dāng)前全球市場(chǎng)ASIC 芯片平均價(jià)格約為3 美元,遠(yuǎn)期若達(dá)到量產(chǎn)規(guī)模,ASIC 芯片價(jià)格有望保持持續(xù)下降態(tài)勢(shì)。

① ASIC 芯片定制化程度較高,設(shè)計(jì)開(kāi)發(fā)周期長(zhǎng),成品需要做物理設(shè)計(jì)和可靠性驗(yàn)證,面市時(shí)間較慢。

② ASIC 芯片對(duì)算法依賴(lài)性較高。人工智能算法高速更新迭代,導(dǎo)致ASIC 芯片更新頻率較高。

③ 因ASIC 芯片定制化程度較高,研發(fā)周期相對(duì)漫長(zhǎng),擴(kuò)大了ASIC 成品被市場(chǎng)淘汰的風(fēng)險(xiǎn)。

① 谷歌于2016 年推出TPU,谷歌旗下2017 版AlphaGo 物理處理器中鑲嵌4 個(gè)TPU,可支持谷歌云TPU 平臺(tái)和機(jī)器學(xué)習(xí)超級(jí)計(jì)算機(jī)。

② IBM 通過(guò)模擬大腦結(jié)構(gòu)于2014 年8 月推出制程為28 納米的第二代TrueNorth芯片,可應(yīng)用于實(shí)時(shí)視頻處理。

③ 英特爾于2017 年推出Xeon 系列ASIC 芯片。該系列芯片可獨(dú)立充當(dāng)處理器,無(wú)需附加主機(jī)處理器和輔助處理器,可應(yīng)用于機(jī)器深度學(xué)習(xí)。

④ 斯坦福大學(xué)推出基于新神經(jīng)形態(tài)計(jì)算架構(gòu)的ASIC 芯片運(yùn)算速度為普通電腦9,000倍,可模擬約100 萬(wàn)個(gè)大腦神經(jīng)元、幾十億個(gè)突觸連接。

⑤ 新興科創(chuàng)企業(yè)將ASIC 芯片應(yīng)用拓展至安防、輔助駕駛、傳統(tǒng)家電、智慧醫(yī)療等領(lǐng)域。

參考來(lái)源:中國(guó)ASIC芯片行業(yè)精品報(bào)告

<服務(wù)器基礎(chǔ)知識(shí)全解(終極版)>,內(nèi)容全面覆蓋,知識(shí)點(diǎn)深度講解,提供182頁(yè)完整版付費(fèi)下載。

獲取方式:點(diǎn)擊“閱讀原文”即可查看詳情,提供PPT可編輯版本和PDF閱讀版本。

溫馨提示:

請(qǐng)搜索“AI_Architect”或“掃碼”關(guān)注公眾號(hào)實(shí)時(shí)掌握深度技術(shù)分享,點(diǎn)擊“閱讀原文”獲取更多精彩技術(shù)干貨。