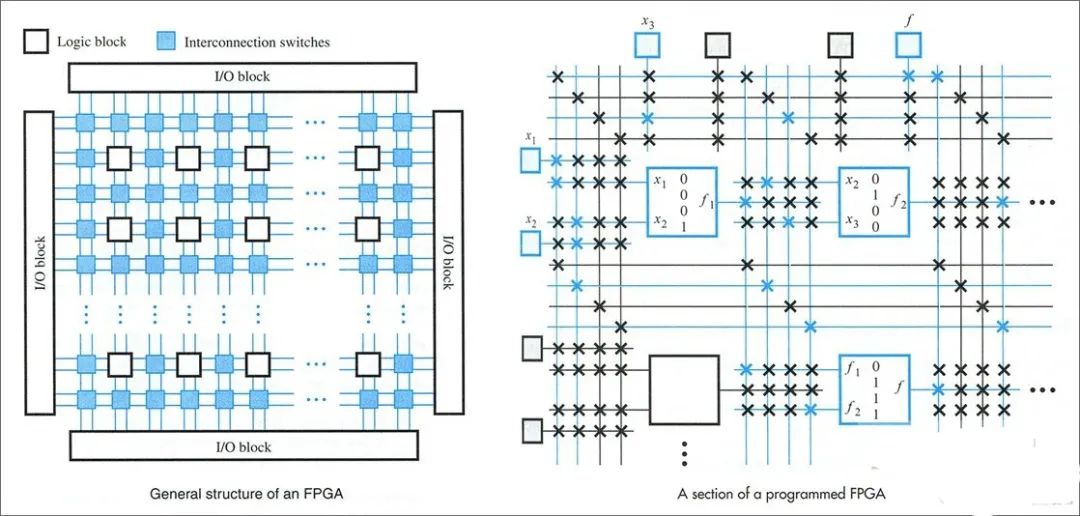

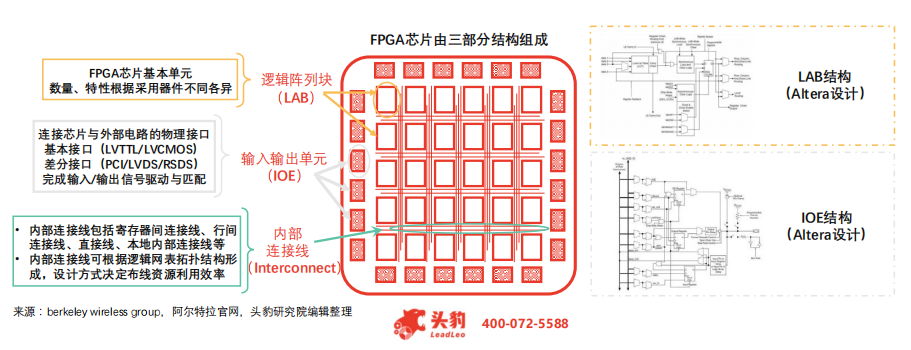

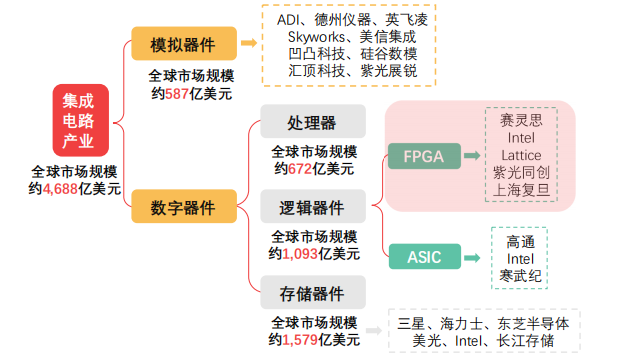

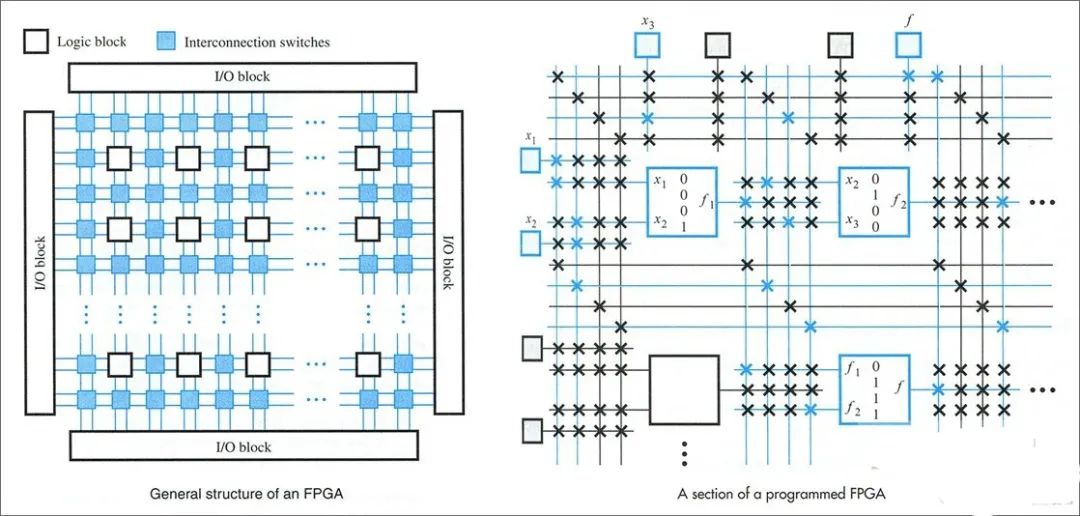

AI芯片主要分為CPU 、GPU、FPGA以及ASIC。其中以CPU、GPU、FPGA、ASIC的順序,通用性逐漸減低,但運(yùn)算效率逐步提高。FPGA即現(xiàn)場(chǎng)可編程門(mén)陣列,它是在PAL、GAL、CPLD等可編程器件癿基礎(chǔ)上迕一步収展的產(chǎn)物。FPGA芯片基于可編程器件(PAL、GAL)發(fā)展而來(lái),是半定制化、可編程的集成電路。發(fā)明者:賽靈思聯(lián)合創(chuàng)始人Ross Freeman于1984年發(fā)明FPGA集成電路結(jié)構(gòu)。全球第一款商用FPGA芯片為賽靈思XC4000系列FPGA產(chǎn)品。FPGA芯片按固定模式處理信號(hào),可執(zhí)行新型任務(wù)(計(jì)算任務(wù)、通信任務(wù)等)。FPGA芯片相對(duì)專用集成電路(如ASIC芯片)更具靈活性,相對(duì)傳統(tǒng)可編程器件可添加更大規(guī)模電路數(shù)量以實(shí)現(xiàn)多元功能。物理結(jié)構(gòu):FPGA芯片主要由三部分組成,分別為IOE(input output element,輸入輸出單元)、LAB(logic array block,邏輯陣列塊,賽靈思定義為可配置邏輯塊CLB)以及Interconnect(內(nèi)部連接線)。FPGA芯片在實(shí)時(shí)性(數(shù)據(jù)信號(hào)處理速度快)、靈活性等方面具備顯著優(yōu)勢(shì),在深度學(xué)習(xí)領(lǐng)域占據(jù)不可替代地位,同時(shí)具有開(kāi)發(fā)難度高的特點(diǎn)。

FPGA芯片具備以下特點(diǎn):

設(shè)計(jì)靈活:屬于硬件可重構(gòu)的芯片結(jié)構(gòu),內(nèi)部設(shè)置數(shù)量豐富的輸入輸出單元引腳及觸發(fā)器。

兼容性強(qiáng):FPGA芯片可與CMOS、TTL等大規(guī)模集成電路兼容,協(xié)同完成計(jì)算任務(wù)。

并行計(jì)算:FPGA內(nèi)部結(jié)構(gòu)可按數(shù)據(jù)包步驟多少搭建相應(yīng)數(shù)量流水線,不同流水線處理不同數(shù)據(jù)包,實(shí)現(xiàn)流水線并行、數(shù)據(jù)并行功能。

適用性強(qiáng):是專用電路中開(kāi)發(fā)周期最短、應(yīng)用風(fēng)險(xiǎn)最低的器件之一(部分客戶無(wú)需投資研發(fā)即可獲得適用FPGA芯片)。

地位提升:早期在部分應(yīng)用場(chǎng)景是ASIC芯片的批量替代品;近期隨微軟等頭部互聯(lián)網(wǎng)企業(yè)數(shù)據(jù)中心規(guī)模擴(kuò)大,F(xiàn)PGA芯片應(yīng)用范圍擴(kuò)大。

FPGA廠商主要提供基于兩種技術(shù)類型的FPGA芯片:Flash技術(shù)類、SRAM技術(shù)類(Static Random-access Memory,靜態(tài)隨機(jī)存取存儲(chǔ)器)。兩類技術(shù)均可實(shí)現(xiàn)系統(tǒng)層面編程功能,具備較高計(jì)算性能,系統(tǒng)門(mén)陣列密度均可超過(guò)1兆。

核心區(qū)別:基于Flash的可編程器件具備非易失性特征,即電流關(guān)閉后,所存儲(chǔ)數(shù)據(jù)不消失。基于SRAM技術(shù)的FPGA芯片不具備非易失性特征,是應(yīng)用范圍最廣泛的架構(gòu)。

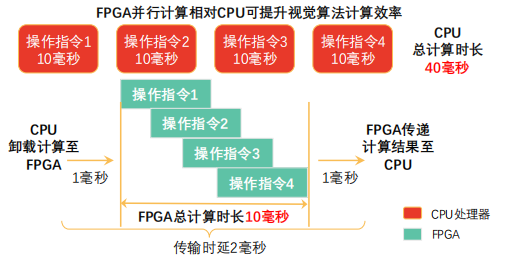

CPU為通用型器件,F(xiàn)PGA架構(gòu)相對(duì)CPU架構(gòu)偏重計(jì)算效率,依托FPGA并行計(jì)算處理視覺(jué)算法可大幅提升計(jì)算速率,降低時(shí)延。

CPU處理計(jì)算指令流程:CPU通過(guò)專用譯碼器接收任務(wù)指令,接收過(guò)程分為兩步:指令獲取(CPU從專門(mén)存放指令的存儲(chǔ)器中提取執(zhí)行指令)以及指令翻譯(根據(jù)特定規(guī)則將指令翻譯為數(shù)據(jù)并傳輸至計(jì)算單元)。其中計(jì)算單元為晶體管(CPU基本元件),“開(kāi)”、“關(guān)”分別對(duì)應(yīng)“1”、“0”機(jī)器碼數(shù)字。CPU物理結(jié)構(gòu)包括Control(指令獲取、指令翻譯)、Cache(臨時(shí)指令存儲(chǔ)器)、計(jì)算單元ALU(約占CPU空間20%)。

CPU為通用型計(jì)算任務(wù)處理核心,可處理來(lái)自多個(gè)設(shè)備的計(jì)算請(qǐng)求,可隨時(shí)終止當(dāng)前運(yùn)算,轉(zhuǎn)向其他運(yùn)算。

邏輯控制單元及指令翻譯結(jié)構(gòu)較為復(fù)雜,可從中斷點(diǎn)繼續(xù)計(jì)算任務(wù),為實(shí)現(xiàn)高度通用性而犧牲計(jì)算效率。

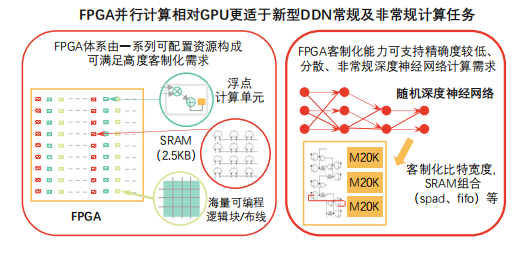

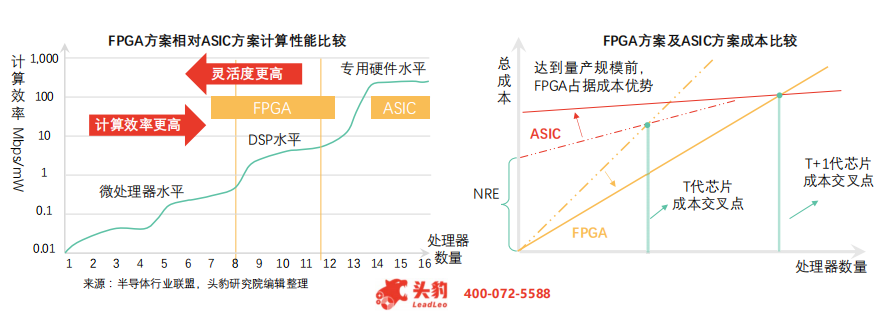

CPU視覺(jué)算法與FPGA視覺(jué)算法比較:? CPU架構(gòu):CPU用于處理視覺(jué)算法需按指定順序執(zhí)行指令,第一指令在圖像整體運(yùn)行完成后,第二指令開(kāi)始運(yùn)行。在4步操作指令環(huán)境下,設(shè)定單個(gè)操作指令運(yùn)行需10毫秒,完成總算法耗時(shí)約40毫秒。 ? FPGA架構(gòu):FPGA用于處理視覺(jué)算法采取規(guī)模化并行運(yùn)算模式,可于圖像不同像素內(nèi)同時(shí)運(yùn)行4步操作指令。設(shè)定單個(gè)操作操作指令運(yùn)行需10毫秒,F(xiàn)PGA完成圖像整體視覺(jué)算法處理時(shí)間僅為10毫秒,F(xiàn)PGA圖像處理速度顯著快于CPU。?“FPGA+CPU”架構(gòu):此架構(gòu)下,圖像在CPU與FPGA之間傳輸,包含傳輸時(shí)間在內(nèi)的算法整體處理時(shí)間仍低于純CPU架構(gòu)。? 算法案例:以卷積濾鏡圖像銳化計(jì)算任務(wù)為例,系統(tǒng)需通過(guò)閾值運(yùn)行圖像生產(chǎn)二進(jìn)制圖像。CPU架構(gòu)下,系統(tǒng)需在閾值步驟前完成圖像整體卷積步驟,F(xiàn)PGA則支持相同算法同時(shí)運(yùn)行,相對(duì)CPU架構(gòu),卷積計(jì)算速度提升約20倍。GPU作為圖形處理器件,計(jì)算峰值較高,遠(yuǎn)期在機(jī)器學(xué)習(xí)領(lǐng)域(多指令平行處理單一數(shù)據(jù)),F(xiàn)PGA相對(duì)GPU在靈活性、功耗方面更勝一籌GPU物理結(jié)構(gòu):GPU為圖形處理器,針對(duì)各類計(jì)算機(jī)圖形繪制行為進(jìn)行運(yùn)算(如頂點(diǎn)設(shè)置、光影操作、像素操作等),標(biāo)準(zhǔn)GPU包括2D引擎、3D引擎、視頻處理引擎、顯存管理單元等。其中,3D引擎包含T&L單元、 PiexlShader等。? 頂點(diǎn)處理:GPU讀取3D圖形頂點(diǎn)數(shù)據(jù),根據(jù)外觀數(shù)據(jù)確定3D圖形形狀、位置關(guān)系,建立3D圖形骨架。 ? 光柵化計(jì)算:顯示器圖像由像素組成,系統(tǒng)需將圖形點(diǎn)、線通過(guò)算法轉(zhuǎn)換至像素點(diǎn)。矢量圖形轉(zhuǎn)換為像素點(diǎn)為光柵化計(jì)算過(guò)程。? 紋理貼圖:通過(guò)紋理映射對(duì)多變形表面進(jìn)行帖圖處理,進(jìn)而生成真實(shí)圖形。? 像素處理:GPU對(duì)光柵化完成的像素進(jìn)行計(jì)算、處理,確定像素最終屬性,多通過(guò)Pixel Shader(像素著色器)完成。?峰值性:GPU計(jì)算峰值(10Tflops)顯著高于FPGA計(jì)算峰值(小于1TFlops)。GPU架構(gòu)依托深度流水線等技術(shù)可基于標(biāo)準(zhǔn)單元庫(kù)實(shí)現(xiàn)手工電路定制。相對(duì)而言,F(xiàn)PGA設(shè)計(jì)資源受限,型號(hào)選擇決定邏輯資源上限(浮點(diǎn)運(yùn)算資源占用較高),F(xiàn)PGA邏輯單元基于SRAM查找表,布線資源受限。? 內(nèi)存接口:GPU內(nèi)存接口(雙倍數(shù)據(jù)傳輸率存儲(chǔ)器等)帶寬優(yōu)于FPGA使用的DDR(雙倍速率同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器)接口,滿足機(jī)器學(xué)習(xí)頻繁訪問(wèn)內(nèi)存需求。? 靈活性:FPGA可根據(jù)特定應(yīng)用編程硬件,GPU設(shè)計(jì)完成后無(wú)法改動(dòng)硬件資源,遠(yuǎn)期機(jī)器學(xué)習(xí)使用多條指令平行處理單一數(shù)據(jù),FPGA硬件資源靈活性更能滿足需求。 ? 功耗:GPU 平 均 功 耗 (200W) 遠(yuǎn) 高 于 FPGA 平 均 功 耗(10W),可有效解決散熱問(wèn)題。ASIC芯片專用度高,開(kāi)發(fā)流程非重復(fù)成本(流片)極高,5G商用普及初期,F(xiàn)PGA可依托靈活性搶占市場(chǎng),但規(guī)模化量產(chǎn)場(chǎng)景下,ASIC芯片更具競(jìng)爭(zhēng)優(yōu)勢(shì)

ASIC與FPGA開(kāi)發(fā)流程區(qū)別:

? ASIC需從標(biāo)準(zhǔn)單元進(jìn)行設(shè)計(jì),功能需求及性能需求發(fā)生變化時(shí),ASIC芯片設(shè)計(jì)需經(jīng)歷重新投片,設(shè)計(jì)流程時(shí)間成本、經(jīng)濟(jì)成本較高。

? FPGA包括預(yù)制門(mén)和觸發(fā)器,具備可編程互連特性,可實(shí)現(xiàn)芯片功能重新配置。相對(duì)而言,ASIC芯片較少具備重配置功能。

ASIC與FPGA經(jīng)濟(jì)成本、時(shí)間成本區(qū)別:

? ASIC設(shè)計(jì)過(guò)程涉及固定成本,設(shè)計(jì)過(guò)程造成材料浪費(fèi)較少,相對(duì)FPGA重復(fù)成本較低,非重復(fù)成本較高(平均超百萬(wàn)美元)。

? FPGA重復(fù)成本高于同類ASIC芯片,規(guī)模化量產(chǎn)場(chǎng)景下,ASIC芯片單位IC成本隨產(chǎn)量增加持續(xù)走低,總成本顯著低于FPGA芯片。

? FPGA無(wú)需等待芯片流片周期,編程后可直接使用,相對(duì)ASIC有助于企業(yè)節(jié)省產(chǎn)品上市時(shí)間。

? 技術(shù)未成熟階段,F(xiàn)PGA架構(gòu)支持靈活改變芯片功能,有助于降低器件產(chǎn)品成本及風(fēng)險(xiǎn),更適用于5G商用初期的市場(chǎng)環(huán)境。

中國(guó)FPGA芯片行業(yè)產(chǎn)業(yè)鏈由上游底層算法設(shè)計(jì)企業(yè)、EDA工具供應(yīng)商、晶圓代工廠、專用材料及設(shè)備供應(yīng)商,中游各類FPGA芯片制造商、封測(cè)廠商及下游包括視覺(jué)工業(yè)廠商、汽車廠商、通信服務(wù)供應(yīng)商、云端數(shù)據(jù)中心等在內(nèi)的應(yīng)用場(chǎng)景客戶企業(yè)構(gòu)成。

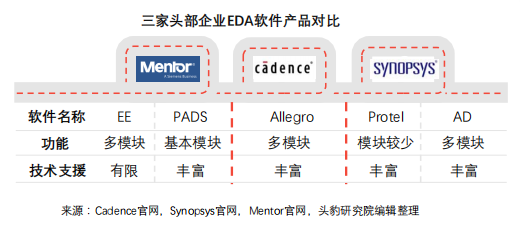

FPGA芯片作為可編程器件,流片需求較少,對(duì)上游代工廠依賴度較低,需專業(yè)設(shè)計(jì)軟件、算法架構(gòu)支持。底層算法架構(gòu)設(shè)計(jì)企業(yè):FPGA芯片設(shè)計(jì)對(duì)底層算法架構(gòu)依賴度較低,上游算法供應(yīng)商對(duì)中游FPGA芯片研發(fā)制造企業(yè)議價(jià)能力有限。境外算法架構(gòu)設(shè)計(jì)企業(yè)包括高通、ARM、谷歌、微軟、IBM等。專用軟件供應(yīng):FPGA芯片企業(yè)需通過(guò)EDA等開(kāi)發(fā)輔助軟件(quartus、vivado等)完成設(shè)計(jì)。可提供EDA軟件的國(guó)際一流企業(yè)(如Synopsys)向芯片研發(fā)企業(yè)收取高昂模塊使用費(fèi)。中國(guó)市場(chǎng)可提供EDA產(chǎn)品的企業(yè)較少,以芯禾電子、華大九天 、博達(dá)微科技等為代表,中國(guó)EDA企業(yè)研發(fā)起步較晚,軟件產(chǎn)品穩(wěn)定性、成熟度有待提高。中國(guó)FPGA芯片研發(fā)企業(yè)采購(gòu)境外EDA軟件產(chǎn)品成本高昂,遠(yuǎn)期有待境內(nèi)EDA企業(yè)消除與境外同類企業(yè)差距,為中游芯片企業(yè)提供價(jià)格友好型EDA產(chǎn)品。晶圓代工廠當(dāng)前中國(guó)主流晶圓廠約30家,在規(guī)格上分別涵蓋8英寸晶圓、12英寸晶圓。其中,8英寸晶圓廠相對(duì)12英寸晶圓廠數(shù)量較多。中國(guó)本土12英寸晶圓廠以武漢新芯、中芯國(guó)際、紫光等為例,平均月產(chǎn)能約65千片。在中國(guó)設(shè)立晶圓廠的境外廠商包括Intel、海力士等。中國(guó)晶圓廠發(fā)展速度較快,如武漢新芯12寸晶圓以平均月產(chǎn)能200千片超過(guò)海力士平均月產(chǎn)能160千片。中國(guó)FPGA芯片行業(yè)中游企業(yè)擁有較大利潤(rùn)空間,隨研發(fā)能力積累及應(yīng)用市場(chǎng)成熟,中游行業(yè)格局或發(fā)生裂變,從發(fā)展硬件、器件研發(fā)業(yè)務(wù)轉(zhuǎn)向發(fā)展軟件、平臺(tái)搭建業(yè)務(wù)。

FPGA芯片產(chǎn)品可快速切入應(yīng)用市場(chǎng),具備不可替代性,現(xiàn)階段應(yīng)用場(chǎng)景較為分散。隨技術(shù)成熟度提升,終端廠商或考慮采用ASIC芯片置換FPGA芯片以降低成本(ASIC量產(chǎn)成本低于FPGA)。

相對(duì)CPU、GPU、ASIC等產(chǎn)品,F(xiàn)PGA芯片利潤(rùn)率較高。中低密度百萬(wàn)門(mén)級(jí)、千萬(wàn)門(mén)級(jí)FPGA芯片研發(fā)企業(yè)利潤(rùn)率接近50%(可參考iPhone毛利率接近50%的水平)。高密度億門(mén)級(jí)FPGA芯片研發(fā)企業(yè)利潤(rùn)率近70%(可以賽靈思、Intel收購(gòu)的阿爾特拉為例)。

隨FPGA行業(yè)中游企業(yè)集中度提高,行業(yè)格局或發(fā)生裂變。中國(guó)企業(yè)可通過(guò)市場(chǎng)策略調(diào)整,從硬件研發(fā)業(yè)務(wù)轉(zhuǎn)向軟件設(shè)計(jì),從器件研發(fā)轉(zhuǎn)向平臺(tái)建設(shè)。

本文選自“中國(guó)FPGA芯片行業(yè)研究報(bào)告”,分為上、下篇分析,本文聚焦報(bào)告前四章節(jié),內(nèi)容目錄和下載地址如下:1、FPGA芯片定義及物理結(jié)構(gòu)4、FPGA芯片行業(yè)產(chǎn)業(yè)鏈5、FPGA芯片行業(yè)市場(chǎng)規(guī)模7、全球FPGA大廠競(jìng)爭(zhēng)8、中國(guó)FPGA芯片行業(yè)驅(qū)動(dòng)因素9、5G通信體系建設(shè)提高FPGA芯片需求10、自動(dòng)駕駛規(guī)模化商用提升量產(chǎn)需求下載鏈接:中國(guó)FPGA芯片行業(yè)報(bào)告

ASIC技術(shù)專題分析

2021中國(guó)智能網(wǎng)卡行業(yè)概覽

免責(zé)申明:本號(hào)聚焦相關(guān)技術(shù)分享,內(nèi)容觀點(diǎn)不代表本號(hào)立場(chǎng),可追溯內(nèi)容均注明來(lái)源,發(fā)布文章若存在版權(quán)等問(wèn)題,請(qǐng)留言聯(lián)系刪除,謝謝。

電子書(shū)<服務(wù)器基礎(chǔ)知識(shí)全解(終極版)>更新完畢,知識(shí)點(diǎn)深度講解,提供182頁(yè)完整版下載。

獲取方式:點(diǎn)擊“閱讀原文”即可查看PPT可編輯版本和PDF閱讀版本詳情。

溫馨提示:

請(qǐng)搜索“AI_Architect”或“掃碼”關(guān)注公眾號(hào)實(shí)時(shí)掌握深度技術(shù)分享,點(diǎn)擊“閱讀原文”獲取更多原創(chuàng)技術(shù)干貨。