臺積電太強(qiáng)了!興建 2nm 生產(chǎn)重鎮(zhèn)、3nm 明年試產(chǎn),推 3D Farbic 封裝平臺

技術(shù)編輯:芒果果丨發(fā)自 思否編輯部

SegmentFault 思否報(bào)道丨公眾號:SegmentFault

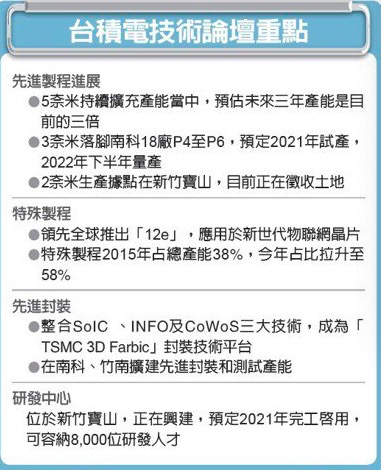

臺積電昨日舉行了線上年度技術(shù)論壇,其總裁魏哲家分享了臺積電的最新技術(shù)進(jìn)展,首度公開宣布,2nm 制程生產(chǎn)重鎮(zhèn)已于新竹寶山動(dòng)工興建,預(yù)計(jì)將于明年修建完成。

有關(guān) 2nm 制程采用的規(guī)格及路徑,臺積電方面并未做出詳細(xì)說明,但強(qiáng)調(diào)了將有別于 3nm 制程。臺積電制程迭代的周期基本保持在兩年,若按此慣例推斷,2nm 制程或?qū)⒂?2024 年推出。

魏哲家還宣布,臺積電已將?SoIC、InFO、CoWoS 等 3D 封裝技術(shù)平臺整合,推出了?TSMC 3D Farbic 平臺。

3 nm、4nm 明年試產(chǎn),2nm 生產(chǎn)重鎮(zhèn)興建

魏哲家在講話中提到,臺積電 7nm 晶圓出貨量已達(dá)到了 10 億,5nm 已經(jīng)進(jìn)入量產(chǎn),4nm 和 3nm 將于明年開始試產(chǎn),2022 年下半年實(shí)現(xiàn)量產(chǎn)。

臺積電3奈米沿用鰭式場效電晶體(FinFET)架構(gòu),據(jù)臺積電公布的數(shù)據(jù),3nm 制程與 5nm 相比,速度提升了 15%,功耗減少了 30%,晶體密度是 5nm 的 1.7 倍。

魏哲家指出,臺積電將繼續(xù)推進(jìn)先進(jìn)制程,4nm 在速度、功耗、密度上更加進(jìn)步,與 5nm 有 100% 的 IP 相容性,可以沿用既有的設(shè)計(jì)基礎(chǔ)、架構(gòu)和產(chǎn)品創(chuàng)新。

臺積電的 2nm 生產(chǎn)重鎮(zhèn)落地新竹寶山,占地 90 多公頃,規(guī)劃了 P1 到 P4 四個(gè)超大型晶圓廠,整個(gè)生產(chǎn)研發(fā)中心預(yù)計(jì)將于明年完工投入使用,屆時(shí)將有 8000 名研發(fā)精英進(jìn)駐。據(jù)了解,臺積電去年的研發(fā)資金接近 30 億美元,今年將持續(xù)擴(kuò)大投資。

全球首創(chuàng)先進(jìn)封裝平臺

此外,魏哲家海宣布,臺積電已將前后段 3D IC 封裝整合成了 TSMC 3D Farbic 平臺,是全球首家具備前段 3D IC 封裝能力的晶圓代工廠。

業(yè)界分析,三星稍早推出的 3D 封裝技術(shù) X-Cube 采用的是矽鉆孔(TSV)進(jìn)行晶圓與晶圓堆疊(WoW)的技術(shù),適用于 7nm 和 5nm 制程生產(chǎn)的晶圓,臺積電的 TSMC 3D Farbic 整合了前段的系統(tǒng)整合單晶片封裝(SoIC)中的晶圓級封裝 CoS 及晶圓堆疊封裝(WoW),和后段的整合扇出型封裝(INFO)及 CoWoS 等復(fù)雜3D封裝技術(shù),使封裝服務(wù)更具整合能力。

臺積電研發(fā)副總余振華將 TSMC 3D Farbic 平臺視為延伸摩爾定律的重要技術(shù)突破。他強(qiáng)調(diào),這個(gè)技術(shù)可以提升系統(tǒng)功能性、縮小晶圓尺寸,并且加快產(chǎn)品上市進(jìn)程。

從臺積電目前滿載的訂單來看,在 5nm 制程上再次勝過了勁敵三星,獨(dú)攬了蘋果新世代A14處理器代工大單。

雖然臺積電對此刻意保持低調(diào),也并未透露 2nm 制程更多細(xì)節(jié),但根據(jù)此前的報(bào)道,臺積電已找到成功路徑,將切入GAA(環(huán)繞閘極)技術(shù),邁向另一項(xiàng)全新的技術(shù)節(jié)點(diǎn)。