三星首代3nm工藝彎道超過(guò)臺(tái)積電:只能說(shuō)互有勝負(fù)

在傳統(tǒng)的印象中,半導(dǎo)體工藝的數(shù)字越小,代表其制造工藝越先進(jìn)。但隨著半導(dǎo)體制造工藝進(jìn)入到14nm節(jié)點(diǎn),傳統(tǒng)的制造工藝命名就開(kāi)始被“玩壞”,制造工藝已經(jīng)變成數(shù)字游戲,也不再被業(yè)界承認(rèn)。

在傳統(tǒng)的印象中,半導(dǎo)體工藝的數(shù)字越小,代表其制造工藝越先進(jìn)。但隨著半導(dǎo)體制造工藝進(jìn)入到14nm節(jié)點(diǎn),傳統(tǒng)的制造工藝命名就開(kāi)始被“玩壞”,制造工藝已經(jīng)變成數(shù)字游戲,也不再被業(yè)界承認(rèn)。 首先是來(lái)自三星官方的說(shuō)法,與5納米工藝(三星5nm)相比,第一代3納米工藝可以降低45%功耗、性能提升23%、芯片面積減少16%。

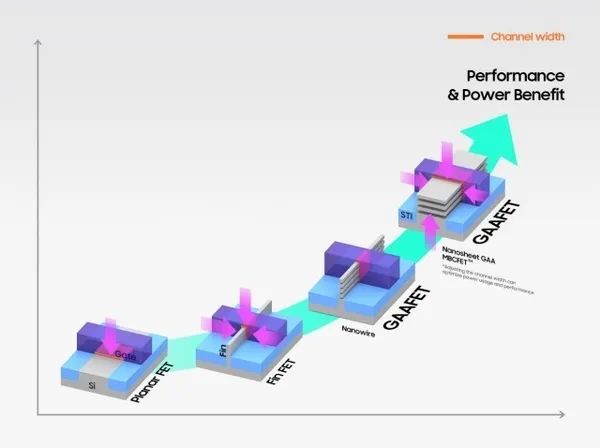

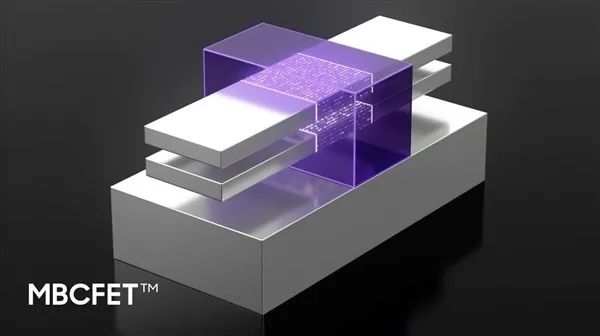

首先是來(lái)自三星官方的說(shuō)法,與5納米工藝(三星5nm)相比,第一代3納米工藝可以降低45%功耗、性能提升23%、芯片面積減少16%。 編輯點(diǎn)評(píng):對(duì)于半導(dǎo)體芯片來(lái)說(shuō),晶體管密度是衡量性能的重要指標(biāo),但并非全部。事實(shí)上,從傳統(tǒng)的MOS晶體管到FinFET晶體管、再到最新的GAA架構(gòu),除了提升晶體管密度外,降低內(nèi)部漏電率、提升處理器運(yùn)行頻率同樣重要。

編輯點(diǎn)評(píng):對(duì)于半導(dǎo)體芯片來(lái)說(shuō),晶體管密度是衡量性能的重要指標(biāo),但并非全部。事實(shí)上,從傳統(tǒng)的MOS晶體管到FinFET晶體管、再到最新的GAA架構(gòu),除了提升晶體管密度外,降低內(nèi)部漏電率、提升處理器運(yùn)行頻率同樣重要。

END

覺(jué)得不錯(cuò)請(qǐng)給我一個(gè)“在看”

評(píng)論

圖片

表情