搶先臺(tái)積電,三星3nm GAA工藝成功流片

目前全球已量產(chǎn)的最先進(jìn)半導(dǎo)體工藝是5nm,臺(tái)積電此前表示,2022年下半年將量產(chǎn)3nm工藝,不過(guò)在3nm節(jié)點(diǎn)臺(tái)積電依然選擇FinFET晶體管技術(shù),而三星則選擇了GAA(Gate-all-around)技術(shù)。近日,三星對(duì)宣布其基于GAA技術(shù)的3nm制程成已成功流片(Tape Out)。

據(jù)外媒報(bào)導(dǎo),三星3nm制程流片進(jìn)度是與新思科技(Synopsys)合作,加速為GAA 架構(gòu)的生產(chǎn)流程提供高度優(yōu)化參考方法。因?yàn)槿腔贕AA技術(shù)的3nm制程不同于臺(tái)積電FinFET架構(gòu)的3nm制程,所以三星需要新的設(shè)計(jì)和認(rèn)證工具,故而采用了新思科技的Fusion Design Platform。

針對(duì)三星3nm GAA制程技術(shù)的物理設(shè)計(jì)套件(PDK)已在2019 年5 月發(fā)表,并2020 年通過(guò)制程技術(shù)認(rèn)證。預(yù)計(jì)此流程使三星3nm GAA 結(jié)構(gòu)制程技術(shù)可用于高性能計(jì)算(HPC)、5G、移動(dòng)和高端人工智能(AI)應(yīng)用芯片生產(chǎn)。

三星代工設(shè)計(jì)技術(shù)團(tuán)隊(duì)副總裁Sangyun Kim 表示,三星代工技術(shù)是推動(dòng)下一階段產(chǎn)業(yè)創(chuàng)新的核心。三星將藉由不斷發(fā)展技術(shù)制程,滿足專業(yè)和廣泛市場(chǎng)增長(zhǎng)的需求。三星電子最新且先進(jìn)的3nm GAA 制程技術(shù),受惠于與新思科技合作,F(xiàn)usion Design Platform 加速準(zhǔn)備,有效達(dá)成3nm制程技術(shù)承諾,證明關(guān)鍵聯(lián)盟的重要性和優(yōu)點(diǎn)。

新思科技數(shù)位設(shè)計(jì)部總經(jīng)理Shankar Krishnamoorthy 也表示,GAA 晶體管結(jié)構(gòu)象征著制程技術(shù)進(jìn)步的關(guān)鍵轉(zhuǎn)換點(diǎn),對(duì)保持下一波超大規(guī)模創(chuàng)新所需的策略至關(guān)重要。新思科技與三星戰(zhàn)略合作支持提供一流技術(shù)和解決方案,確保發(fā)展趨勢(shì)延續(xù),以及為半導(dǎo)體產(chǎn)業(yè)提供機(jī)會(huì)。

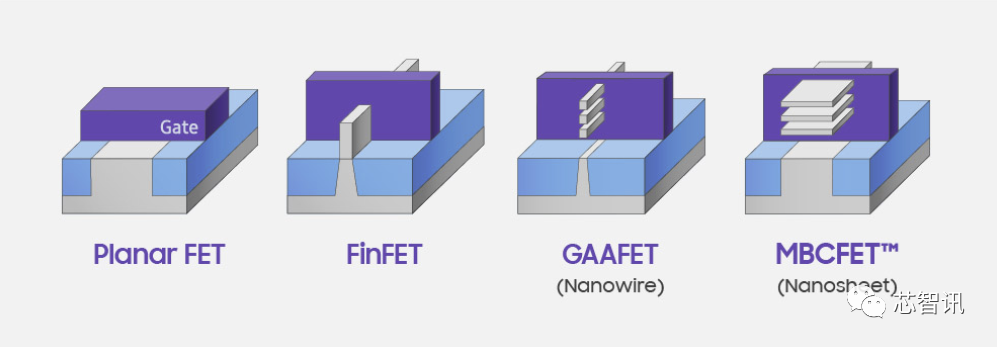

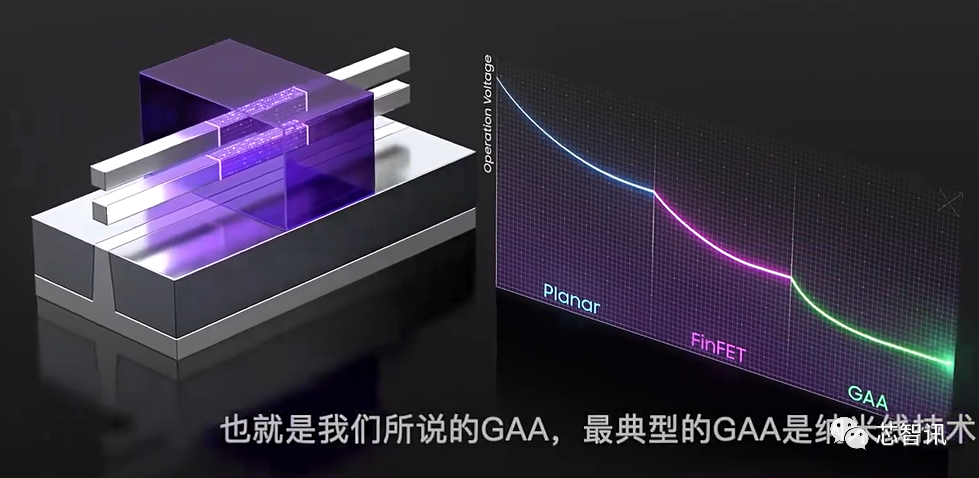

傳統(tǒng)的平面晶體管(Planar FET)通過(guò)降低電壓來(lái)節(jié)省功耗,然而,平面晶體管的短溝道效應(yīng)限制了電壓的繼續(xù)降低,而FinFET(鰭式場(chǎng)效應(yīng)晶體管)的出現(xiàn)使得電壓得以再次降低,但隨著工藝的繼續(xù)推進(jìn),F(xiàn)inFET已經(jīng)不足以滿足需求。于是,GAA(Gate-all-around,環(huán)繞柵極)技術(shù)應(yīng)運(yùn)而生。

如下圖,典型的GAA形式——GAAFET是(Gate-all-around FETs)采用的是納米線溝道設(shè)計(jì),溝道整個(gè)外輪廓都被柵極完全包裹,代表柵極對(duì)溝道的控制性更好。相比之下,傳統(tǒng)的FinFET 溝道僅3 面被柵極包圍。GAAFET 架構(gòu)的晶體管提供比FinFET 更好的靜電特性,可滿足某些柵極寬度的需求。這主要表現(xiàn)在同等尺寸結(jié)構(gòu)下,GAA 的溝道控制能力強(qiáng)化,尺寸可以進(jìn)一步微縮。

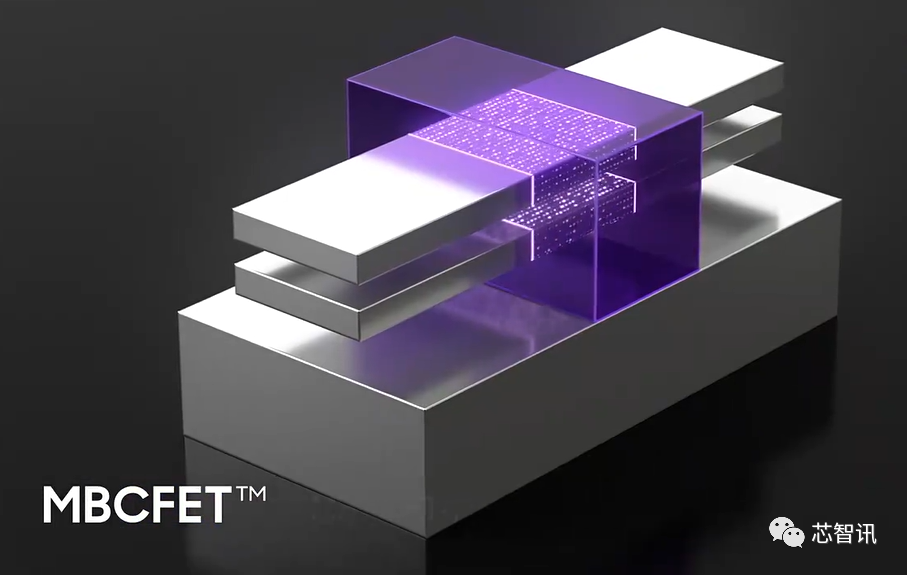

不過(guò),三星認(rèn)為采用納米線溝道設(shè)計(jì)不僅復(fù)雜,且付出的成本可能也大于收益。因此,三星設(shè)計(jì)了一種全新的GAA形式——MBCFET(Multi-Bridge-Channel FET,多橋-通道場(chǎng)效應(yīng)管),采用多層堆疊的納米片來(lái)替代GAAFET中的納米線。這種納米片設(shè)計(jì)已被研究機(jī)構(gòu)IMEC當(dāng)作FinFET 架構(gòu)后續(xù)產(chǎn)品進(jìn)行大量研究,并由IBM 與三星和格羅方德合作發(fā)展。

三星表示,MBCFET可以在保留所有GAAFET優(yōu)點(diǎn)的情況下,最小化復(fù)雜度。同時(shí),MBCFET的設(shè)計(jì)可以兼容之前的FinFET技術(shù),可以直接將為FinFET的設(shè)計(jì)遷移到MBCFET上,在不提升面積的情況下,提升性能。

此外,在制造環(huán)節(jié),此技術(shù)也具高度可制造性,因?yàn)槠淅眉s90% FinFET 制造技術(shù)與設(shè)備,只需少量修改的光罩即可。

三星稱,MBCFET出色的柵極可控性,比三星原本FinFET 技術(shù)高出了31%,且納米片通道寬度可直接圖像化改變,設(shè)計(jì)更有靈活性。

三星的3nm GAA(MBCFET)工藝分為3GAAE / GAAP (3nm Gate- AlI-Around Early/Plus)兩個(gè)階段。按照三星的說(shuō)法,與5nm工藝相比,3nm GAA技術(shù)的邏輯面積效率提高了35%以上,功耗降低了50%,性能提高了約30%。

隨著此次三星3nm GAA制程的成功流片,則意味著距離三星3nm GAA工藝的量產(chǎn)又近了一步。根據(jù)三星此前的預(yù)計(jì),可能會(huì)在2022年量產(chǎn)。

對(duì)于臺(tái)積電來(lái)說(shuō),其在3nm制程上依然采用了FinFET技術(shù),等到2nm節(jié)點(diǎn)才會(huì)采用GAA技術(shù),路線應(yīng)該是納米線溝道設(shè)計(jì)的GAAFET架構(gòu)。目前臺(tái)積電正在進(jìn)行先進(jìn)材料和晶體管結(jié)構(gòu)的預(yù)研。

另外,臺(tái)積電還加強(qiáng)先導(dǎo)性研發(fā)工作,重點(diǎn)放在2nm以外節(jié)點(diǎn),以及3D晶體管、新記憶體、low-R interconnect 等領(lǐng)域,有望為許多技術(shù)平臺(tái)奠定生產(chǎn)基礎(chǔ)。臺(tái)積電還在擴(kuò)大Fab 12 的研發(fā)能力,目前Fab 12 正在研究開發(fā)N3、N2 甚至更高階制程節(jié)點(diǎn)。

編輯:芯智訊-浪客劍

翱捷科技科創(chuàng)板IPO過(guò)審:自研5G芯片已成功流片,最快年底量產(chǎn)!

募資35億!龍芯中科科創(chuàng)板IPO獲受理:全面掌握CPU指令系統(tǒng)等核心技術(shù)

馬來(lái)西亞全國(guó)封鎖無(wú)限期延長(zhǎng),封測(cè)產(chǎn)能及被動(dòng)元件供應(yīng)或再受打擊

概倫電子科創(chuàng)板IPO獲受理:客戶遍及臺(tái)積電、三星等大廠,英特爾是第7大股東!

中國(guó)廠商全球爆買半導(dǎo)體制造設(shè)備:每類設(shè)備多買5~6臺(tái)當(dāng)庫(kù)存

芯片短缺仍未緩解,平均交期已拉長(zhǎng)至18周!終端價(jià)格將持續(xù)上漲

90%市場(chǎng)被國(guó)外壟斷!從華大九天招股書,看國(guó)產(chǎn)EDA產(chǎn)業(yè)現(xiàn)狀

行業(yè)交流、合作請(qǐng)加微信:icsmart01

芯智訊官方交流群:221807116