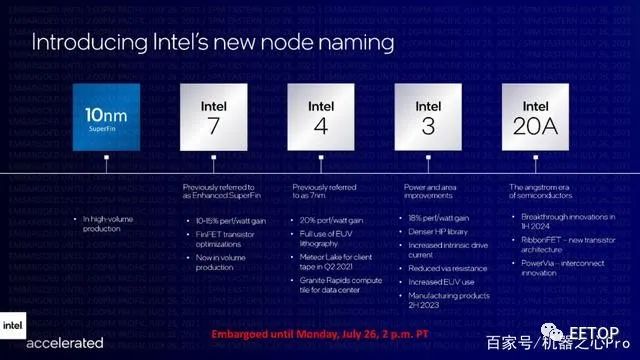

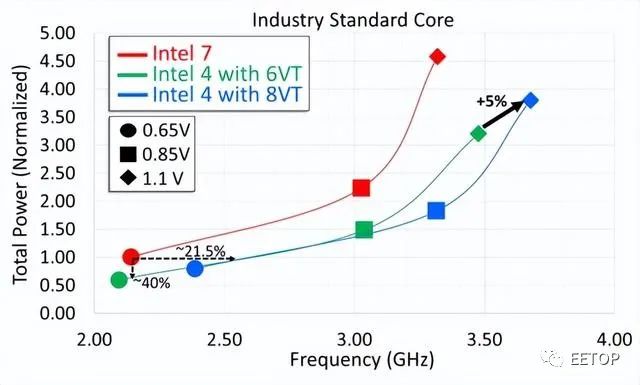

Intel 4工藝細節(jié)曝光:較上代性能提升21%、功耗降低40%

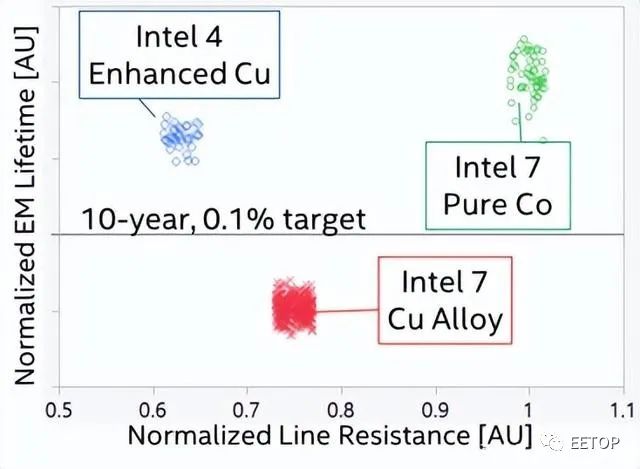

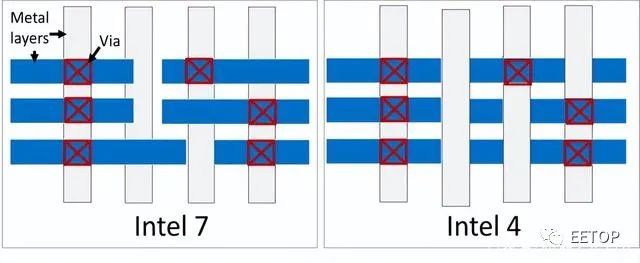

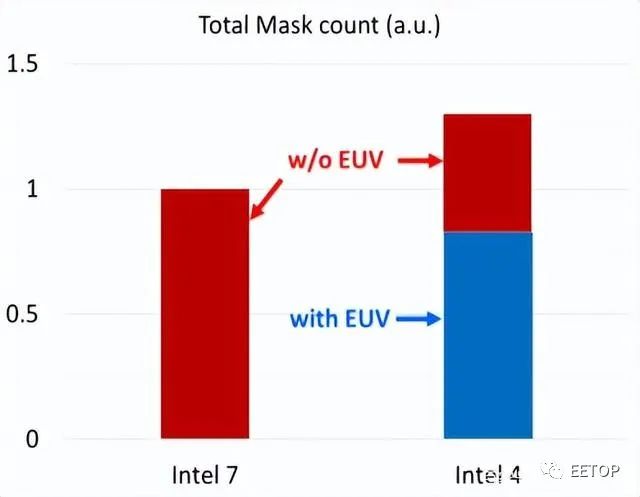

對于英特爾來說,Intel 4 是一個重要的里程碑,它既是英特爾第一個集成 EUV 的工藝,也是第一個跳出陷入困境的 10nm 節(jié)點的工藝。

免責申明:本號聚焦相關(guān)技術(shù)分享,內(nèi)容觀點不代表本號立場,可追溯內(nèi)容均注明來源,發(fā)布文章若存在版權(quán)等問題,請留言聯(lián)系刪除,謝謝。

電子書<服務(wù)器基礎(chǔ)知識全解(終極版)>更新完畢。

獲取方式:點擊“閱讀原文”即可查看182頁 PPT可編輯版本和PDF閱讀版本詳情。

溫馨提示:

請搜索“AI_Architect”或“掃碼”關(guān)注公眾號實時掌握深度技術(shù)分享,點擊“閱讀原文”獲取更多原創(chuàng)技術(shù)干貨。

評論

圖片

表情